FFT实时谱分析系统的FPGA设计和实现

摘要: 采用按时间抽选的基4原位算法和坐标旋转数字式计算机(CORDIC)算法实现了一个FFT实时谱分析系统。整个设计采用流水线工作方式,保证了系统的速度,避免了瓶颈的出现;整个系统采用FPGA实现,实验表明,该系统既有DSP器件实现的灵活性又有专用 FFT芯片实现的高速数据吞吐能力,可以广泛地应用于数字信号处理的各个领域。

关键词: 快速傅里叶变换 CORDIC算法 现场可编程门阵列(FPGA)

快速傅里叶变换(Fast Fourier Transformation, FFT) 实时谱分析是DSP应用的核心技术之一,而在高速实时信号处理中,常采用专门集成电路(ASIC)来实现。FPGA是一种具有大量的可编程逻辑单元的器件,它的应用使得电子产品不仅具有高速度、高集成度和高可靠性,而且具有用户可编程特性,能降低设计风险。实验表明,用FPGA实现的实时谱分析系统既有专用ASIC电路实现的快速性,又有DSP器件实现的灵活性,非常适用于高速实时的数字信号处理。

1 FFT实时信号处理系统的总体设计

FFT频谱分析系统主要由1024点基-4 FFT模块和接口控制电路组成。其中,基-4 FFT模块用于实现一组1024点复数数据的FFT变换;接口控制电路负责控制1024点基-4 FFT模块,并对A/D采样输出的数据进行缓存、速率匹配等,协调整个FFT频谱分析系统的工作时序。

在本设计中,FFT实时谱分析系统的1024点基-4 FFT算法采用FPGA实现。FPGA的总体框图如图1所示。其中,衰减限幅模块负责对数据进行衰减及限幅压缩处理;双口RAM负责存储外部输入的原始数据及经过蝶形运算后的中间数据;四点FFT模块完成4点DFT运算;地址控制模块负责产生读地址、写地址、写使能信号以及相关模块的启动、控制信号,是FFT系统的控制核心;复乘运算模块是系统运算的核心部分,采用CORDIC算法实现;旋转因子产生器产生复乘运算中的旋转因子的角度数据;倒序模块实现频谱正常顺序输出。

2 功能模块的设计

2.1 衰减限幅模块

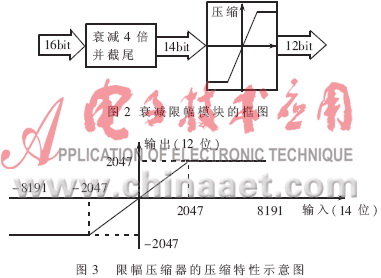

FFT实时谱分析系统采用的算术运算方案是定点运算,衰减限幅模块实现了定比例衰减、尾数处理和压缩信号电平的作用,用以防止数据溢出。模块框图如图2所示,其压缩特性如图3所示。

2.2 四点FFT模块

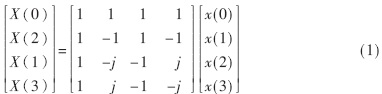

四点FFT模块完成四点DFT变换,变换公式如下:

四点FFT模块中完全不需要复数乘法,乘-j只需将实部虚部交换,再加上必要的正负号即可。四点FFT模块采用流水线工作方式,每四个时钟周期完成一组四点FFT运算。在输入一组四点原始数据x(i)时,要完成两项工作:①进行上一组四点FFT的第二级运算,即计算并输出上一组四点FFT的结果X(k);②进行本组四点FFT的第一级运算,即计算本组四点FFT的中间结果X′(k)。这样充分利用了硬件资源。

2.3 复乘运算模块

复乘运算是FFT处理器中两种最频繁的运算之一,因而复乘运算模块也是FFT处理器中的一个重要模块。输入复数数据xr+jxi与旋转因子cosα+jsinα相乘的公式为:

利用CORDIC的圆周旋转的向量工作模式可以实现复乘运算,所采用的迭代方程组如下:

所以,只需将需要运算的角度值作为z0输入,经过旋转迭代后,迭代结果的xn和yn就是所需要的旋转因子 复乘的运算值。即:

复乘的运算值。即:

复乘运算模块的工作流程如图4所示。

从复乘运算的算法流程中可以看到,实现复乘运算的主要元件有加法器、移位器和多选一数据选择器等。组成流水线后,各流水单元结构相似,很适合用FPGA实现。

2.4 旋转因子产生模块在一个基-4蝶形运算单元中,包含WP、W2P和W3P三个旋转因子,每组基-4蝶形运算的第一个输出数据所乘的旋转因子总为1。在同一个蝶形组内,p值是不变的,因而只需确定一个p值,三个旋转因子便可确定下来。每当一个基-4蝶形组计算完毕而转入下一个蝶形组时,p值改变一次,其变化的顺序恰好是(L-1)位四进制数顺序加1的倒序输出。由此可以根据蝶形运算的级数和四点FFT的节点位置计算出对应的旋转因子的角度。

由于

=cos(

=cos( )-jsin(

)-jsin( ),在程序中将小数cos(

),在程序中将小数cos( )和-sin(

)和-sin( )转换成定点数,变换为二进制数进行计算。

)转换成定点数,变换为二进制数进行计算。本设计的复乘运算采用CORDIC算法实现,需要输入角度值作为进行复乘运算的相应旋转因子的角度,因此旋转因子产生模块输出的数据即对应旋转因子的角度值,模块中包括10位计数器和一个计算输出进程。程序的运算流程如图5所示。

本设计采用直接计算旋转因子的方法,不需要产生旋转因子的读取地址和额外的ROM资源,简化了设计,但需要一直进行角度值的计算,增加了系统的运算时间。

3 FFT实时频谱分析系统的实现

本设计采用Synplicity公司的逻辑综合软件Synplify7.1 pro进行设计综合,用Xilinx的ISE6.1布局布线。实现后的系统的时序分析结果表示,系统有9.139ns的延迟,系统时钟周期可达10.817ns,系统频率达到92.4MHz。当系统频率为90MHz时,1024点FFT运算需要的时间大约为68.3μs,完全可以满足实时处理的要求。本文采用Xilinx公司的Virtex-Ⅱxc2v500 fg456-5 FPGA器件实现系统,设计使用资源状况如表1所示。

FPGA 快速傅里叶变换 CORDIC算法 FFT 相关文章:

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)