基于DSP Builder的DDS设计及其FPGA实现

时间:11-03

来源:21ic

点击:

直接数字合成器,是采用数字技术的一种新型频率合成技术,他通过控制频率、相位增量的步长,产生各种不同频率的信号。他具有一系列的优点;较高的频率分辨 率;可以实现快速的频率切换;在频率改变时能够保持相位的连续;很容易实现频率、相位和幅度的数控调制等。目前可采用专用芯片或可编程逻辑芯片实现DDS [1],专用的DDS芯片产生的信号波形、功能和控制方式固定,常不能满足具体需要[2]。可编程逻辑器件具有器件规模大、工作速度快及可编程的硬件特 点,并且开发周期短,易于升级,因为非常适合用于实现DDS。

1 DDS的工作原理

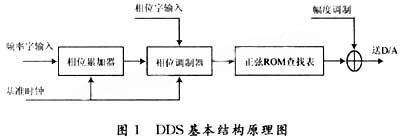

DDS的结构原理图如图1所示,DDS以数控振荡器的方式,产生频率、相位和幅度可控的正弦波[3]。电路包括了相位累加器、相位调制器、正弦ROM查找表、基准时钟源、D/A转换器等组成。其中前三者是DDS结构中的数字部分,具有数控频率合成的功能。

DDS系统的核心是相位累加器,完成相位累加过程。在基准时钟的控制下,频率控制字由累加器累加,以得到相应的相位数据,相位调制器接收相位累加器的相位 输出,主要用于信号的相位调制,其输出的数据作为取样地址来寻址正弦ROM查找表,完成相位-幅度变换,输出不同的幅度编码;再经过D/A转换器得到相应 的阶梯波;最后经低通滤波器对阶梯进行平滑处理,即可得到由频率控制字决定的连续变换输出的正弦波。

2 基于DSP Builder和DDS设计

2.1 DSP Builder简介

DSP Builder是美国Altera公司推出的一个面向DSP开发的系统级工具,他作为Matlab的一个Simulink工具箱,使得用FPGA 设计DSP系统完全通过Simulink的图形化界面进行建模、系统级仿真,设计模型可直接向VHDL硬件描述语言转换,并自动调用QuartusⅡ等 EDA设计软件,完成综合、网表生成以及器件适配乃至FPGA的配置下载,使得系统描述与硬件实现有机的融合为一体,充分体现了现代电子技术自动化开发的 特点与优势。

2.2 DSP Builder设计原理及参数设置

基于DSP Builder的DDS系统如图2和图3所示,DDS子系统Subsystem有3个输入,分别为Freqword(32位频率控制字)、 Phaseword(32位相位控制字)、Amp(10位幅度控制字);一个输出,即10位DDSOut输出。2个 Parallel Adder Subtractor分别为相位累加器和相位调制器,LUT为正弦ROM查找表。设置Simulink的仿真停止时间 stop time为5,仿真步进Fixed Step Size为le-3。图(4)对应频率、相位和幅度控制字分别为4000000,0和10(参数 1)时DDS系统的输出波形,图5对应频率、相位和幅度控制字分别为9000000,500000000和15(参数2)时DDS系统的输出波形。

3 基于FPGA的DDS设计

3.1 DDS的FPGA实现

Matlab/Simulink对已经设计好的DDS系统进行编译,通过调用DSP Builder的SignalCompiler工具可直接生成QuartusⅡ 工程文件,再调用QuartusⅡ完成综合,网表生成和适配,直至完成FPGA的配置下载过程。

本设计方案采用的FPGA芯片是Altera公司的Cyclone系列芯片EP1C6Q240C8,,其容量6000个逻辑宏单元,等效于标准15万逻辑 门电路,速度为-8,完成可通过单片芯片电路实现DDS,相位累加和相位调制器均为32位,正弦ROM查找表存储1024×10b波形数据,系统时钟为 55.6MHz,利用FPGA可以根据需要方便地实现各种比较复杂的调频,调相和调幅功能,具有浪费的实时性。

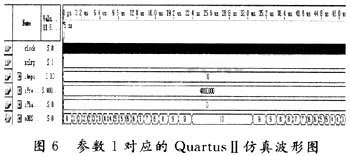

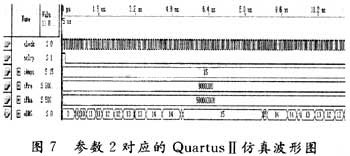

使用QuartusⅡ对DSP builder生成的工程文件进行仿真,针对不同参数设置的DDS系统,其仿真波形图如图6和图7所示。

图中,clock为系统时钟,sclrp为高电平复位信号,iFreqwords,iPhasewords和iAmps分别为输入频率、相位和幅度控制 字,oDDSOut为输出信号。当复位信号sclrp到来后,向相位累加器赋0,并向相位调制器赋一个初始相位值,在时钟信号的控制下,频率控制字控制相 位累加器累加,相位调制器进行相位调制,其输出数据作为取样地址寻址ROM查找表,便可以在oDDSOut管脚上输出连续的正弦波信号。在不同的参数设置 下,QuartusⅡ中的仿真结果与Matlab/Simulink中的仿真结果在相位,频率和幅度上基本一致。利用FPGA能输出较高质量的信号,虽然 内部数字信号有一定的抖动,但通过采用抖动注入技术、延时叠加法等[3]方法,通常也能将误差保持在允许范围之内。

4 结论

利用可编程逻辑芯片设计DDS的方法通常是采用VHDL语言输入和原理图法相结合来设计整个信号发生电路,这种方法通常需要调用很多模块,综合性较强,对 设计者要求较高。本文利用QuartusⅡ和Matlab/Simulink之间的接口工具DSP Builder来设计整个DDS系统, DSP Builder具备一个友好的开发环境,并且和QuartusⅡ交互性强,易于使用。设计者只需简单了解VHDL描述语言,就可以直接调用已经建 立好的Matlab和Simulink设计流程,通过Simulink的图形化界面进行建模、系统级仿真,并子对调用QuartusⅡ进行综合,网表生成 和适配,最后完成向FPGA的配置下载过程。整个设计思路灵活,图形界面简单直观,开发周期短。仿真结果表明,该设计方案原理正确,行之有效。用FPGA 实现DDS较专用DDS芯片更为灵活,只要改变FPGA中ROM内的数据和控制参数,DDS就可以产生任意调制波形,且分辨率高,具有相当大的灵活性。将 DDS设计嵌入到FPGA芯片所构成的系统中,其系统成本并不会增加多少,而购买专用芯片的价格则是前者的很多倍。所以采用FPGA设计DDS系统具有很 高的性价比。

1 DDS的工作原理

DDS的结构原理图如图1所示,DDS以数控振荡器的方式,产生频率、相位和幅度可控的正弦波[3]。电路包括了相位累加器、相位调制器、正弦ROM查找表、基准时钟源、D/A转换器等组成。其中前三者是DDS结构中的数字部分,具有数控频率合成的功能。

DDS系统的核心是相位累加器,完成相位累加过程。在基准时钟的控制下,频率控制字由累加器累加,以得到相应的相位数据,相位调制器接收相位累加器的相位 输出,主要用于信号的相位调制,其输出的数据作为取样地址来寻址正弦ROM查找表,完成相位-幅度变换,输出不同的幅度编码;再经过D/A转换器得到相应 的阶梯波;最后经低通滤波器对阶梯进行平滑处理,即可得到由频率控制字决定的连续变换输出的正弦波。

2 基于DSP Builder和DDS设计

2.1 DSP Builder简介

DSP Builder是美国Altera公司推出的一个面向DSP开发的系统级工具,他作为Matlab的一个Simulink工具箱,使得用FPGA 设计DSP系统完全通过Simulink的图形化界面进行建模、系统级仿真,设计模型可直接向VHDL硬件描述语言转换,并自动调用QuartusⅡ等 EDA设计软件,完成综合、网表生成以及器件适配乃至FPGA的配置下载,使得系统描述与硬件实现有机的融合为一体,充分体现了现代电子技术自动化开发的 特点与优势。

2.2 DSP Builder设计原理及参数设置

基于DSP Builder的DDS系统如图2和图3所示,DDS子系统Subsystem有3个输入,分别为Freqword(32位频率控制字)、 Phaseword(32位相位控制字)、Amp(10位幅度控制字);一个输出,即10位DDSOut输出。2个 Parallel Adder Subtractor分别为相位累加器和相位调制器,LUT为正弦ROM查找表。设置Simulink的仿真停止时间 stop time为5,仿真步进Fixed Step Size为le-3。图(4)对应频率、相位和幅度控制字分别为4000000,0和10(参数 1)时DDS系统的输出波形,图5对应频率、相位和幅度控制字分别为9000000,500000000和15(参数2)时DDS系统的输出波形。

3 基于FPGA的DDS设计

3.1 DDS的FPGA实现

Matlab/Simulink对已经设计好的DDS系统进行编译,通过调用DSP Builder的SignalCompiler工具可直接生成QuartusⅡ 工程文件,再调用QuartusⅡ完成综合,网表生成和适配,直至完成FPGA的配置下载过程。

本设计方案采用的FPGA芯片是Altera公司的Cyclone系列芯片EP1C6Q240C8,,其容量6000个逻辑宏单元,等效于标准15万逻辑 门电路,速度为-8,完成可通过单片芯片电路实现DDS,相位累加和相位调制器均为32位,正弦ROM查找表存储1024×10b波形数据,系统时钟为 55.6MHz,利用FPGA可以根据需要方便地实现各种比较复杂的调频,调相和调幅功能,具有浪费的实时性。

使用QuartusⅡ对DSP builder生成的工程文件进行仿真,针对不同参数设置的DDS系统,其仿真波形图如图6和图7所示。

图中,clock为系统时钟,sclrp为高电平复位信号,iFreqwords,iPhasewords和iAmps分别为输入频率、相位和幅度控制 字,oDDSOut为输出信号。当复位信号sclrp到来后,向相位累加器赋0,并向相位调制器赋一个初始相位值,在时钟信号的控制下,频率控制字控制相 位累加器累加,相位调制器进行相位调制,其输出数据作为取样地址寻址ROM查找表,便可以在oDDSOut管脚上输出连续的正弦波信号。在不同的参数设置 下,QuartusⅡ中的仿真结果与Matlab/Simulink中的仿真结果在相位,频率和幅度上基本一致。利用FPGA能输出较高质量的信号,虽然 内部数字信号有一定的抖动,但通过采用抖动注入技术、延时叠加法等[3]方法,通常也能将误差保持在允许范围之内。

4 结论

利用可编程逻辑芯片设计DDS的方法通常是采用VHDL语言输入和原理图法相结合来设计整个信号发生电路,这种方法通常需要调用很多模块,综合性较强,对 设计者要求较高。本文利用QuartusⅡ和Matlab/Simulink之间的接口工具DSP Builder来设计整个DDS系统, DSP Builder具备一个友好的开发环境,并且和QuartusⅡ交互性强,易于使用。设计者只需简单了解VHDL描述语言,就可以直接调用已经建 立好的Matlab和Simulink设计流程,通过Simulink的图形化界面进行建模、系统级仿真,并子对调用QuartusⅡ进行综合,网表生成 和适配,最后完成向FPGA的配置下载过程。整个设计思路灵活,图形界面简单直观,开发周期短。仿真结果表明,该设计方案原理正确,行之有效。用FPGA 实现DDS较专用DDS芯片更为灵活,只要改变FPGA中ROM内的数据和控制参数,DDS就可以产生任意调制波形,且分辨率高,具有相当大的灵活性。将 DDS设计嵌入到FPGA芯片所构成的系统中,其系统成本并不会增加多少,而购买专用芯片的价格则是前者的很多倍。所以采用FPGA设计DDS系统具有很 高的性价比。

- DDS函数信号发生器的优点(09-28)

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 基于AD9858的线性调频源设计(11-03)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 基于DDS技术的声纳信号模拟器(01-25)