利用FPGA实现原型板原理图的验证

首次流片成功取决于整个系统硬件和相关软件的验证,有些公司提供的快速原型生成平台具有许多调试功能,但这些平台的价格非常高,因此最流行的做法是根据DUT和具体应用设计复合FPGA板,验证这些板的原理图通常是很麻烦的,本文提出一种利用FPGA实现原型板原理图验证的新方法。

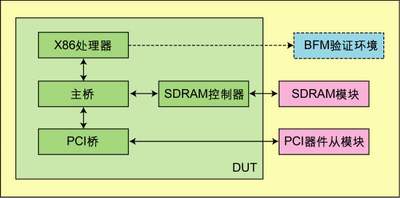

图1:DUT由x86处理器、主桥(Host Bridge)、

SDRAM控制器和PCI桥组成。

由 于价格竞争越来越激烈,首次流片成功或只需少量的修改变得越来越重要。为了达到这一目标,对整个系统(即硬件和相关软件)的验证成为重中之重。业界也涌现 了许多策略来帮助设计师完成RTL上的软件运行。这些策略提供了在最终硬件还在酝酿之时就开发软件的一种途径。这种措施也许还不够,原因还有两个:一是仿真系 统可能与实际系统有较大的区别,二是系统运行速度非常慢。因此可以考虑先将完整的设计映射到FPGA中,再运行目标应用程序。这样做可能达不到最终硅片的 常规指标,但可以测试整个硬件的功能,系统能够得到全面的验证,其中一些测试案例可能是在仿真中根本无法完成的。另外,可用于演示的完整系统原型在硅片成 功之前就可以很好地引起客户的兴趣。

有些公司提供的快速原型生成平台具有许多调试功能。这些电路板平台具有可编程的互连,可以将FPGA插接在上面,并将DUT(被测设计)映射进这些FPGA中。但这些平台的价格非常高。因此最流行的做法还是根据DUT和具体应用设计复合FPGA板。当然,这些板同样也能用于测试目标应用中的最终硅片。

验 证这些板的原理图通常是很麻烦的,因为原理图中一些小错误会严重影响到设计进度。原理图验证工作是人工完成的,因此错误也就在所难免。如果能够复用DUT 验证环境验证电路板原理图,那么原理图验证就可以派上用场了。本文将讨论如何通过编写少量脚本和修改DUT验证环境达到这一目的。

方法简介

基 本想法是设法对原理图进行仿真。这了做到这一点,先将原理图网表转换成Verilog网表。电路板上安装的不同元件(如FPGA、处理器、PCI卡、 SDRAM等)要么用RTL代替,要么用RTL验证过程中使用的行为模型替代。值得注意的是,我们已假设整个设计的Verilog/VHDL代码是现成 的。至于电路板上需要用于测试DUT的处理器、SDRAM、PCI器件等其它元件,也假设已经存在相应的BFM(总线功能模型)/模型。由于这一阶段是在 功能验证之后,而这些元件需要用来测试DUT,并模拟整个系统,因此它们的等效行为模型应该在功能验证中已经得到使用,现在只是重复使用罢了,即经过少许 的努力就能使用相同的环境和测试案例。

上述概念经过拓展就可以验证硅片生成板的原理图,基本的假设是设计团队拥有硅片的 HDL描述。这才是要点所在。对于FPGA板,可以通过某种变通的方法配置FPGA引脚来克服由于原理图中的错误连接导致的问题,即设计师可以管理并解决 这些错误。但对于准备用来测试最终硅片的板子来说几乎是不可能的。

生成Verilog网表

图2:包含x86处理器芯片、2个FPGA、

SDRAM和1个PCI槽道的原型板。

可以用好几种原理图输入工具生成Verilog网表。基于以下几种限制原因,这种网表实际上是不能使用的:

1.它将板上的每个元件都看作是一个模块,因此生成的Verilog文件中包含所有元件的实例,如FPGA、电容、上拉电阻或晶振,而不管这些元件能否在Verilog中建模。其中有些元件(如串接电阻、去耦电容)可以简单地从网表中删除。

2. 原理图中的总线通常被连接到符号上的一个个引脚,而在Verilog模块中总线可能只有一个端口。因此可能没有一对一的对应关系。例如在Verilog模 块中一个四位输出地址总线将被声明为:output [3:0] Address;但原理图中所有这四个引脚是被独立声明的。这样会导致原理图中使用的符号的引脚输出与Verilog模块中相应符号的可用功能不兼容。

因此,设计师需要编写一个简单的脚本,要么修改这个Verilog网表,要么根据原理图输入工具支持的其它格式创建一个新的网表。目的是删除电阻、电容、电感等模拟元件,或用等效的Verilog代码替换它们。

为了更好地实现这一目的,可以利用对模拟元件的命名惯例,或将它们定义在一个文件中作为脚本的输入。例如,电阻可以被命名为R1、R23等,不遵循这个命名惯例的元件可以被定义在约束文件中,这样脚本就可以将它们关联到等效模型,或假定短路将它们从网表中去除。

一般来说,针对电路板上的不同元件可以采用以下一些惯例:

1. 元件的大多数电源引脚可以被忽略。

2. 通常电容都是用作去耦

- 编写属于自己的PCB设计规则检查器(11-06)

- 在电路测试阶段使用无铅PCB表面处理工艺的研究和建议(11-07)

- 使用采样示波器对PCB进行串扰分析(11-06)

- PCB厚密板线路检查LED光源系统研究(11-26)

- 以太网在雷电浪涌测试中的应用(01-19)

- 在线测试技术的现状和发展(04-02)