基于FPGA的2M误码测试仪系统的设计方案

时间:12-10

来源:互联网

点击:

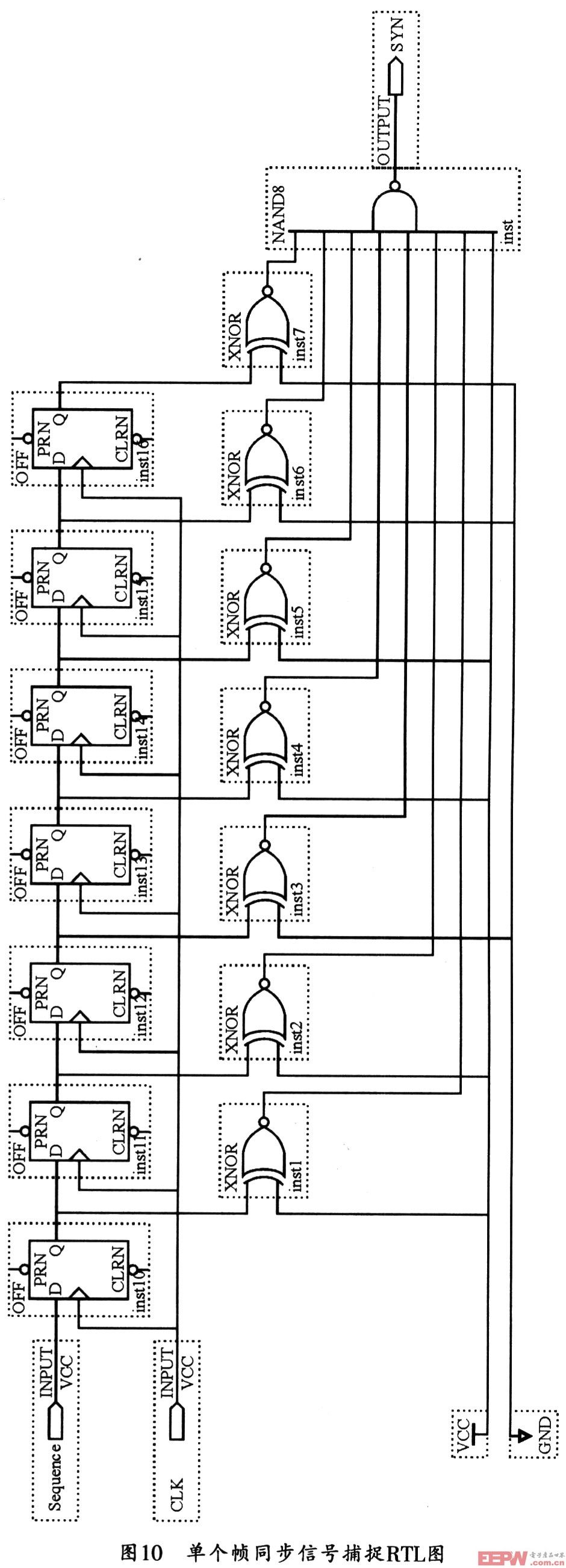

在单个帧同步序列捕捉的FPGA实现中,“0011011”序列的捕捉由输入序列移位寄存器、相关运算阵列和相关求和网络等部分组合完成。工作时,帧同步码序列“0011O11”首先进入相关运算阵列,而输入数据流则在时钟驱动下被送入输入序列移位寄存器中。在相关运算阵列对输入序列和帧同步码进行一次相关运算后,可将结果送入求和网络。输入序列移位寄存器每更新一位数据,相关运算阵列就进行一次相关运算,而求和网络则对每次的结果都进行求和计算。求和网络输出的相关值需要与一个检测门限值作比较,以判断是否出现同步码。检测同步码“001 1011”的模块如图10所示,它由7个触发器、7个异或非门和一个8输入与非门构成。该电路可以检测出sequence串行输入的数据流中包含的特殊码字“0011011”,其中利用地线和电源线可将相关运算阵列的一个输入自右向左的连接成“0011011”,与同步码字对应的另一个输入端接输入序列移位寄存器的输出,7个对应位可进行异或非(同或)运算,对应位匹配时,结果为“1”。7个异或非门的运算结果进入求和网络后,只有当7位对应位全都匹配时,捕捉信号SYN才有效(有效状态为“0”),此时表明找到了一次同步序列码。 4 结束语 本文所介绍的误码测试系统采用以大规模现场可编程逻辑器件FPGA及外围接口芯片构成,文中详细介绍了系统硬件架构中EI接口电路以及FPGA内核中序列发生模块和序列接收模块中核心内容的设计方法,并给出了部分模块的仿真波形。整个误码测试系统仪器结构紧凑。实验表明,该系统在线检测的速度和稳定度方面都有大的提高。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)