基于DSP和FPGA的汽车防撞高速数据采集系统

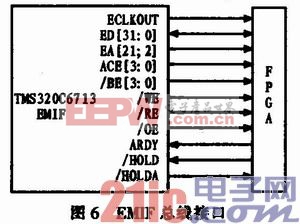

在完成对EMIF的DSP配置后,接下来就是实现EMIF接口的FPGA配置工作,保证FPGA中的数据正常的读入到DSP中。在FPGA中配置EMIF接口的连接图如图7所示。

该模块是DSP与FPGA进行通信的接口模块。通过该模块,DSP可以实现向FPGA传输控制信号,FPGA也可以通过该模块将FIFO中的数据传给DSP。CE、WE、RE、OE为DSP输入的使能信号,CLK为FPGA提供内部时钟,CLKOUT2是EMIF的输出时钟,为DSP与FPGA通信提供时钟频率,DSP_Addr(19:0)为DSP的输入地址,DSP_DataBus(31:0)为DSP的数据总线。FPGA根据读使能信号OE与片选信号CE的输入逻辑来判断EMIF是进行读操作还是写操作。当DSP通过EMIF读取数据时,FPGA中的数据从dpram_data(31:0)输入,由DSP_DataBus(31:0)管脚传送给DSP;若写数据,将DSP_DataBus(31:0)传来的数据从dout(31:0)送入FPGA。

2.4 人机交互模块

人机交互模块分为按健电路和LCD显示电路。限于篇幅,本文仅介绍LCD电路。

LCD显示部分我们采用真空荧光显示点阵式VFD屏,其优点是能高亮度发光。由于我们选择的屏是5 V供电,所以由DSP过来的3.3 V的信号线需要经过74LVCA245转化为5 V,再与VFD屏的控制器接口相连,LCD控制器接口如图8所示。

本系统软件主要由DSP和FPGA组成。其中DSP由系统初始化部分;系统功能模块的EMIF模块,FLASH模块和SDRAM模块组成以及人机交互模块组成。而FPGA设计则由FIFO模块以及DCM模块组成,软件总体模块框图如图9所示。

在整个系统中,DSP芯片负责DSP系统初始化部分和系统功能模块两个部分。其中DSP系统初始化部分包括DSP引导程序,DSP芯片中各硬件寄存器的设置,以及EDMA,定时中断等寄存器的设置。而系统功能模块中,包括FLASH模块和SDRAM模块,由于本系统中DSP需要处理的数据容量比较大,自身的存储容量不够,所以一些数据需要存储于FLASH中,而在运行过程中,很多数据的处理也要在SDRAM中进行;而DSP EMIF模块主要用来连接FPGA,FLASH和SDRAM。

FPGA逻辑设计部分包括了AD逻辑设计,DCM逻辑设计以及FIFO模块的逻辑设计。这块功能设计的主要目的是利用FPGA的硬件逻辑模块,同时进行2路高速AD数据的采集,并将数据放至由ISE软件的IPcore生成的FIFO中,最后由FIFO再通过由与EMIF相对应的逻辑接口将数据传输到DSP中。而整个逻辑设计过程中,其时钟均由DCM模块来产生,DCM模块可以由ISE软件的IPcore来生成,可以通过IP core生成系统需要的时钟频率,有延时少,抖动小等优点。

最后人机交互程序主要是包括LCD模块以及键盘模块。其中LCD来对数据进行显示,而键盘模块来对系统的各个参数进行设定。

4 结束语

文中在对目前高速数据采集系统的发展状况、FPGA可编程控制器件和DSP数字信号处理系统的深入研究的基础上,采用了高速ADC+FPGA+ DSP的设计方案,设计了一款高速数据采集系统,能够用于高速行驶的汽车防撞报警设备中,实时检测目标汽车与障碍物之间的距离,及时提醒驾驶员要提高警惕,注意安全驾驶。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)