基于DSP和FPGA的汽车防撞高速数据采集系统

摘要:随着信息技术的不断发展,数据采集技术已成为重要的现代化的工具,并且其应用范围也在不断扩大,在通信、雷达、医疗、遥测遥感等领域得到了广泛的应用。本文为了汽车防撞报警设备高速信号处理的目的,采用了DSP和FPGA处理器加上相关算法,实现了对激光雷达回波信号能够高速的采集和处理。

关键词:TMS320C6713;FPGA;高速;数据采集

随着人们生活水平的提高,公路上的私家车辆也增多了,但随之带来的问题就是交通事故发生率居高不下,严重危害着人们的生命安全。文中就如何预防交通事故发生,研究设计一种响应迅速、高可靠性并且经济实用的汽车防擅报警设备。该设备在设计过程中的关键任务是利用置于汽车车头左右两端的双路通道高速采集激光雷达回波信号并对其进行实时存储和处理,进而快速测量自身交通工具与障碍物之间的距离及相对速度。

1 系统概述

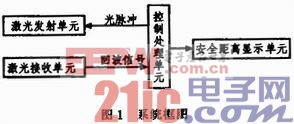

对用于高速公路中的雷达系统而言,考虑到开车的速度比较快,对于一些突发事件无法立刻做出响应,因此就要求设计的防撞雷达探测距离尽量长些,可让驾驶员提前做好安全准备工作,因此这种高速公路防撞系统一般选用激光探测法。采用激光测距的汽车防撞系统结构图,如图1所示。

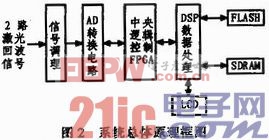

对于激光雷达回波信号经过光电器件转换后形成的电信号,其信号频率高,脉冲宽度相对比较窄,信号幅度低,背景噪音大,如果是选用低速的数据采集系统进行数据采集的话,那么将会存在数据精度不高的不足,所以必须采用高采样率、高分辨率的数据采集系统。系统总体原理框图如图2所示。

该系统的主要信号流程:由激光传感器获得的2路激光雷达回波信号先通过缓冲放大等前端调理后,同时送到AD转换电路进行模数转换,然后可以同时被中央逻辑控制模块FPGA来采集,这样相对于用DSP的分时采集来说,极大的提高了速度。FPGA一方面完成对A/D的采样控制,另一方面与DSP的EMIF接口形成传输通道,完成了AD与DSP之间的数据传输任务,避免了ADC直接与DSP通信,降低了对大量的数据传输的压力。

2.1 前端信号调理电路

2.1.1 前端放大电路

从传感器中输出的信号必须经过调理才能够有效地进行数据采集,为了达到最高的测量精度,应该使被测信号的电压变化范围放大至ADC最大量程附近,所以需要将传感器出来的小信号通过前端放大电路线性放大成适合系统的的电信号。在本系统中主要选用了AD公司生产的AD8062低成本的运放模块来实现的,如图3所示。

2.1.2 前端差分电路

为了消除偶次谐波分量,抑制共模噪声源,起到系统抗干扰的效果,本系统的AD转换电路采用差分输入的形式,而信号经过放大电路后得到的是单端信号,所以,必须要将前端的输入单端信号转化为差分信号。本设计选用了ADI公司生产的AD8620驱动芯片构成差分驱动电路,其具体电路设计如图4所示。

2.2 AD转化电路

在数据采集系统中AD是比较重要的环节,主要完成对激光回波信号的采集工作,而采样时钟信号可以由FPGA电路内部的时钟模块来提供。ADI公司的AD9481,可以采用差分输入,采样率达到250 MSPS,并且采用250 M的PECL标准的时钟信号,为此在设计中为产生该差分时钟信号,考虑选用MC100LEL16的时钟芯片。AD9481的数字输出属于并行接口,有16位的数据流,对于这么高速的数据与存储会出现竞争冒险,使系统不稳定,因此在设计时AD与FPGA的输出端之间串接了一个100 Ω的电阻,可以消除出现在0~1之间的毛刺与高速数据线之间的干扰,具体的AD硬件原理如图5所示。

2.3 数据处理部分硬件电路

本系统数据处理部分由FPGA和DSP两个部分来完成。根据前一级AD电路的信号输出时序进行VHDL编程,来实现同时对两路AD输出的数字信号的采集,将数据输入到FIFO模块中,然后通过EMIF总线将数据快速传输到DSP里进行相关算法的运算。

2.3.1 FPGA电路

FPGA采用硬件编程实现复杂的逻辑功能,不仅能够对采集到的大批量数据流进行预处理,而且作为整个控制系统的核心部分,提供系统所需的时钟信号,保证数据的有序采集,而且作为数据传输的纽带,保证了AD与DSP进行数据传输。结合采样存储传输等功能FPGA的模块主要分为4个部分:时钟管理模块、A/D控制模块、FIFO缓存模块、与DSP的EMIF接口模块:

1)时钟管理模块,该部分主要是产生系统所需的各模块的时钟信号,本系统采用ISE软件自带的DCM模块来实现。

2)A/D控制器:根据当前选择的采样模式为A/D提供相应的控制信号以使A/D正常工作;并通过AD电路的信号输出时序将AD输出的数字信号进行采集。

3)FIFO缓存模块:主要实现将高速采集到的数据缓存到FIFO中。当缓存满时,FIFO的满标志(full)向DSP申请中断,DSP相应中断后采用DMA传输方式把采样效据读到内存中进行数据实时处理。

4)与DSP的EMIF接口模块:DSP通过EMIF接口与FPGA内部的RAM连接,实现了将FPGA中缓存的数据与DSP进行高速传输的作用。

2.3.2 DSP与FPGA的接口设计

本系统在设计中DSP主要是通过C6713器件的外部存储器接口EMIF与FPGA进行数据通信。外部存储器接口(EMIF)是TMS DSP器件上的一种接口。一般来说,EMIF可实现DSP与不同类型存储器(SRAM、Flash RAM、DDR-RAM等)的连接。用EMIF与FPGA相连,从而使FPGA平台充当一个协同处理器、高速数据处理器或高速数据传输接口。

其EMIF的总线接口图如图6所示。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)