基于NI智能FPGA板卡的通用数据采集系统设计

寄存器,同时复位内部RAM的写信号WR(置“0”);在接收周期,控制器按照时钟节拍,接收ADC上一次转换的14 b串行数据;在存储周期,控制器使能WR信号(置“1”),并将接收到的数据写入ADC通道对应的RAM单元;在空闲周期,控制器复位WR信号(置“0”)。

3.2 LabVIEW程序设计

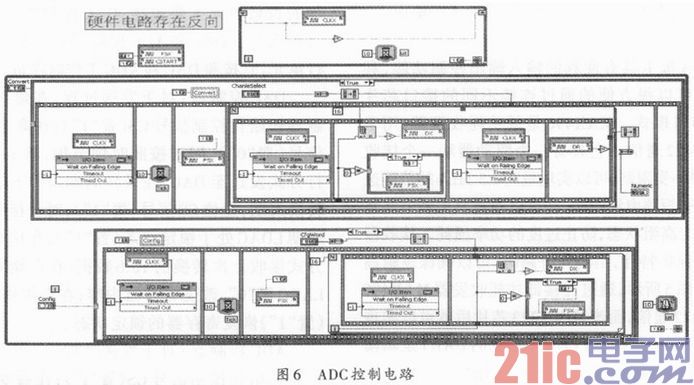

根据FPGA内部的逻辑单元结构和功能,通过NI公司的LabVIEW图形化编程开发平台对上述逻辑进行了设计,并进行了功能仿真。给出ADC控制器LabVIEW程序实现,如图6所示。

NI公司的LabVIEW图形化编程开发平台具有一系列的优点,它不同于VHDL等基于时序的语言,而是一种基于信号流向的语言,程序运行过程和真实硬件电路运行原理相似,用LabVIEW编程的过程就像设计电路图一样。另外它有不需要预先编译就存在语法检查和调试过程使用的数字探针,其丰富的函数、数值分析、信号处理和设备驱动等功能,都是十分优越的。LabVIEW将广泛的数据采集、分析与显示功能集中在了同一个环境中,可以在自己的平台上无缝地集成一套完整的应用方案。

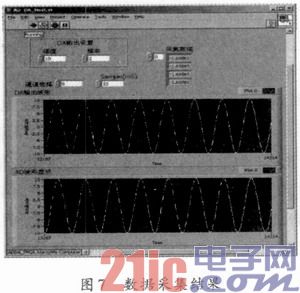

将由LabVIEW图形化编程开发平台通过FPGA生成的正弦信号经D/A电路输出,经过A/D电路进行采集。分别选定四路不同的D/A通道和A/D通道进行输出和输入显示,图形一致,程序运转正常,波形显示清晰。限于DAC和ADC转换速度,采集到的波形存在着微小的相位延迟。如图7所示。

4 结语

基于NI公司FPGA板卡设计和实现的通用数据采集系统原理简单,易于实现。该系统可靠性、实时性、快速性比较好,使得数据处理能力得到了极大的提高,可完全胜任大容量、高精度数据的高速采集。对于采集到的信号可以进行实时处理或保存,也可通过串行口将其送至上位机进行后续分析处理。对于不同应用场合,在FPGA的逻辑单元足够的情况下可以很简便地依据实际情况对其做相应调整,具有较强的通用性,实用价值比较高。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)