基于NI智能FPGA板卡的通用数据采集系统设计

综合考虑系统的分辨率、通道数、采样率、采样范围和接口等要求,系统的ADC选用TI公司的14位8通道高性能逐次逼近型模数转换器TLC3574。该器件工作频率高达25 MHz,采用伪差分的模拟输入电路,将采样信号的动态范围扩展为±10V,其内含的采样和保持功能使得外围电路大为简化。在输出接口上,该器件采用SPI/DSP兼容的串行接口方式,从而极大地减少了接口的连线数量。A/D转换电路原理如图4所示,由FPGA生成TLC3574的SPI接口和时序信号,控制其将外部的模拟信号转换后输入到FPGA,进行相应的计算和处理。由于TLC3574片内没有电压基准,可选用TI公司的三端可凋分流基准源TL431组成外围电路为其提供一个高精度的4 V电压基准。

考虑到信号的阻抗匹配需要,ADC的输入前端需要有一个缓冲运放,其性能必须与ADC的性能相匹配,否则会影响和限制ADC的性能。在数据采集过程中如果信号的变化幅度比较大,则需要根据信号的变化相应调整放大器的增益。否则,单一的增益放大会使得放大后的信号幅值很有可能超过ADC的转换量程。这里所采集的信号其变化幅度不是很大,采用TI公司高转换率的输入端运算放大器TL084就可以满足系统的使用要求。

2.3 数字量输入/输出设计

直接将通用背板的FPGA端口引到前端接口板,根据测试对象的接口电路,如27 V/开、地/开等形式,选择继电器、OC门、光耦隔离等方式,实现数字量的输入和输出。

2.4 串口电路设计

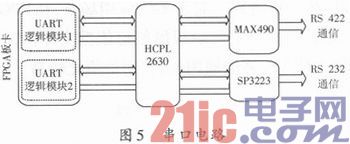

由于FPGA板卡具有便利的输入输出控制功能,利用FPGA板卡可以很方便的通过连接不同的接口芯片选择相应的串口模式。MAX490是低功耗收发器,用于RS 485与RS 422通信。它具有一个驱动器和一个接收器,驱动器摆率不受限制,可以实现最高2.5 Mb/s的传输速率。驱动器具有短路电流限制,并可以通过热关断电路将驱动器输出置为高阻状态,防止过度的功率损耗。接收器输入具有失效保护特性,当输入开路时,可以确保逻辑高电平输出。如图5所示,通过连接低功耗收发器MAX490可以实现RS 422通信,而改接SP3223芯片后就可以实现RS 232通信,区别只是在于FPGA中建立的UART逻辑模块有所不同,进一步显示了系统良好的通用性。

2.5 电气隔离设计

由于该系统为模拟/数字混合信号系统,电路中的噪声会对数模和模数转换精度造成影响,因此在电路的实现上应该对板卡芯片进行降噪和隔离保护,这样既避免了不同信号之间的相互影响,提高了系统的共模抑制能力,也使得一些比较昂贵的芯片不会因为外部信号的不稳定而烧毁。

传统的隔离方式是对每个通道都使用电容耦合模拟隔离芯片ISO124等进行隔离。这类隔离方式其输入和输出分别由两组直流电源供电,而且存在较大的漂移,输出信号通常存在纹波,尤其当信号比较小时,输出的相对误差会增大。因此,还需要对输出信号进行滤波、调零等调理措施,使得系统电路比较复杂。

光电耦合器性能优越,具有良好的抗干扰能力,因而被广泛地应用于输入和输出信号的电气隔离。使用HCPL2630等高速光耦进行光耦隔离,只需要一组直流供电电源,电路十分简单。其良好的电绝缘能力和抗干扰能力使得模拟地和数字地分开,消除了共模电压影响。系统选用串行而非并行的ADC和DAC,只需要隔离三路的SPI总线数字信号,这样进一步简化了电路设计。

3 软件设计

3.1 FPGA逻辑

FPGA智能板卡是整个数据采集系统的核心,由其产生和发送DAC与ADC的SPI接口和工作时序。其内部的逻辑单元主要包括:DAC控制器、ADC控制器、接口单元等。DAC和ADC控制器是FPGA内部的主要执行单元,它按照DAC和ADC工作时序进行相应的工作。

DAC控制器:对于发送过程,在建立周期,DAC控制器初始化控制信号CS(置“1”);在命令周期,使能CS信号(置“0”),同时按照时钟节拍,将16 b命令字以串行方式发送至DAC;在采样周期,对CS信号进行保持;转换周期,置位CS信号(置“1”);对于接收过程,在建立周期LDAC处于锁定状态(置“1”);在接收周期,以串行方式接收上次转换的16 b数据;在存储周期,控制器将LADC置“0”,改变寄存器内容;在空闲周期,复位LADC(置“1”)恢复寄存器的锁定状态。

ADC控制器:对于发送过程,在建立周期,ADC控制器初始化控制信号CS(置“1”);在命令周期,使能CS信号(置“0”),同时按照时钟节拍,将16 b命令字以串行方式发送至ADC;在采样周期,对CS信号进行保持;在转换周期,置位CS信号(置“1”),并载入下一通道的命令字,同时,计算下一次接收数据的存储地址。对于接收过程,在建立周期,控制器清零各接收

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)