频率合成器的设计

在各类无线接收机中,有用信息隐含在载波调制的视频信号中,为了解调出这些信号,通常需要对较高频的载波信号进行一次或二次变频处理,得到幅度、带宽稳定的预解调信号。变频处理的核心是混频与滤波,因此,作为混频本振信号的稳定性和相位噪声对接收机性能影响非常大,频率合成器的设计成为接收机设计的关键课题之一。

频率合成的方法有3类:晶振直接频率合成法、间接频率合成法(即锁相频率合成法)、直接数字合成法。

1 晶振直接频率合成法

晶振直接频率合成器是最早出现的合成器类信号源,它的主要优点是:分辨率高、频率转换速度快、工作稳定可靠、输出信号频谱纯度高。主要缺点是:频率范围有限、体积大,目前在接收机中已很少使用。

2 锁相频率合成法

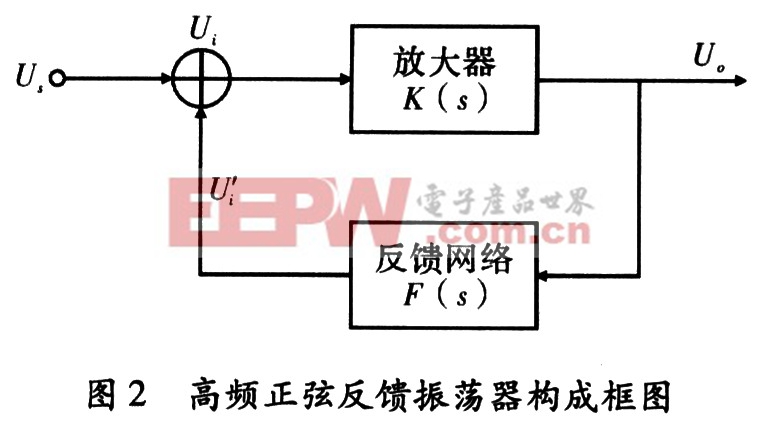

锁相频率合成(PLL)是基于锁相环路的同步原理,从一个高准确度、稳定度的参考晶体振荡器综合出大量的离散频率的技术。图1是工程中使用PLL技术完成频率合成设计的实例。

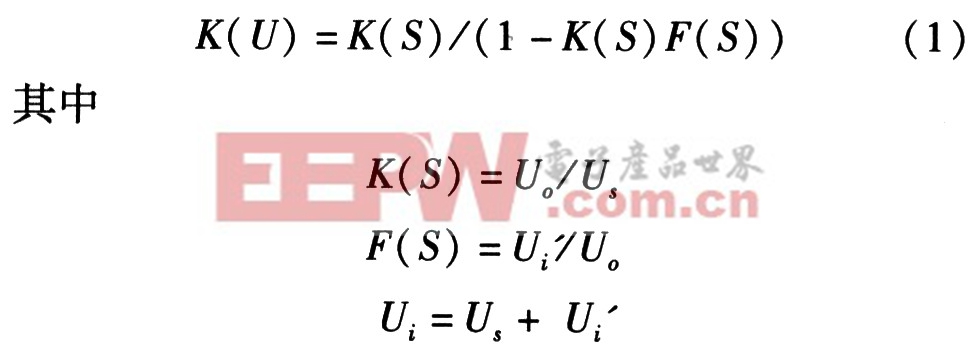

其中,K(S)为放大器的电压放大倍数,F(S)为反馈网络的电压反馈系数,由式(1)可得到此反馈放大器的电压传输系数或称闭环增益。

基于以上公式经分析可知,设计放大器电路只要保证K(S)F(s)为1的正实数,就可使闭环增益K(U)比开环增益K(S)要大,形成正反馈。当在某一频率使得K(S)F(S)=1时,K(U)将趋于无穷大,表明即使没有外加信号,也可维持振荡输出。

3 直接数字合成法

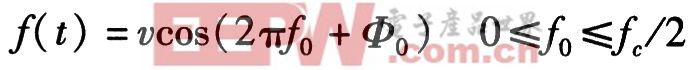

直接数字合成的概念可以理解为数字信号处理理论的一种延伸,可以看作是数字信号处理中信号综合的硬件实现问题。它的主要理论依据是时域抽样定理,即Nyquist定理。根据Nyquist定理,对于任意一个频带fc/2的连续信号f(t),如果以Tc=1/fc的间隔对它进行等间隔抽样,则所得到的离散抽样值包含着连续信号f(t)的全部信息,即通过这些抽样可以恢复f(t)。下面以余弦信号合成为例说明直接数字合成的原理。

一个理想的余弦信号可表示为

它由振幅v,频率f0和初始相位ψ0唯一确定。由于实际合成某一所需频率的余弦信号时与其初始相位无关,幅度是一个比较容易控制的参量,为分析简化起见可假设其振幅v=1,初始相位ψ0=0,即

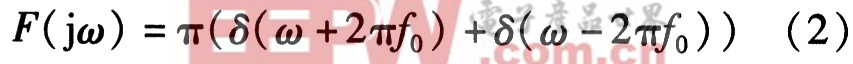

余弦信号的频谱可表示为

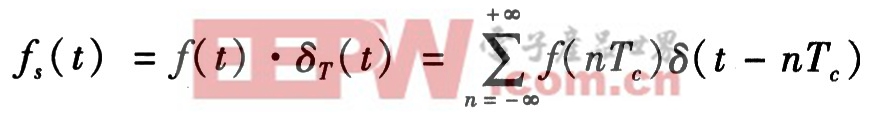

根据抽样定理,如果以fc为抽样频率对f(t)进行抽样,那么得到的抽样信号为

式中 为理想抽样信号,δ(t)为单位冲击函数。抽样信号fs(t)对应的频谱可表示为

为理想抽样信号,δ(t)为单位冲击函数。抽样信号fs(t)对应的频谱可表示为

所以,构造如图3(c)所示的波形,可以从构造一个频率为

所以,构造如图3(c)所示的波形,可以从构造一个频率为 的余弦序列相对应的相位序列着手。

的余弦序列相对应的相位序列着手。

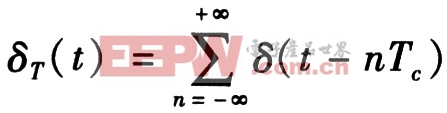

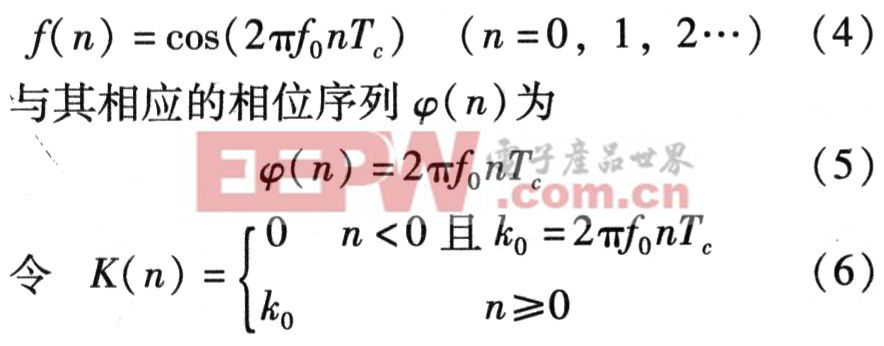

观察离散序列f(nTc),由于Tc为一常数,该序列可写作

即K0为连续两次采样之间的相位增量△ψ,并可得相位序列和K(n)的差分方程

ψ(n)-ψ9(n-1)=K(n-1)

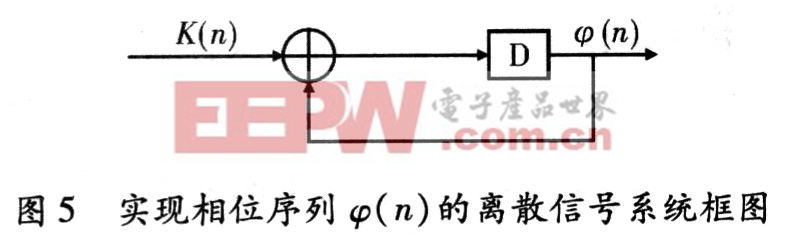

其系统模型,如图5所示,这是以K(n)为激励序列,ψ(n)为响应序列构成的一个离散信号系统,这是一个线性系统。不难看出相位序列的实现过程实质上是一个相位增量K0进行线性累加的过程。

在工程实践中,可采用相位累加器来实现上述的相位累加过程。相位累加器结构,如图6所示,它用N位数字全加器和Ⅳ位数字寄存器构成,K为输入参数,用以改变每次累加的相位增量。

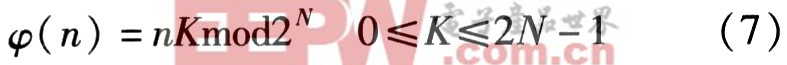

相位累加器的工作过程为:每当一个采样时钟脉冲到来时,加法器就将输入参数K与寄存器输出的数据相加,相加后的结果再送至寄存器。当相位累加器累积满量时,就会产生一次溢出,从而完成一个周期性的累加动作。由相位累加器的值所构成的相位序列可表示为

在相位累加器中,如果采用N位字长的数字寄存器来存储正弦波形一个周期内的抽样后的离散相位,这实际上是对[0,2π]的相位区间进行N位字长的线性量化,其等效结果是使输入参数K和相位增量K0之间建立了一个一一映射的关系

累加器的累加周期即是DDS合成信号的一个频率周期,其值为2N/K个时钟周期。因此合成信号的频率为

这就是DDS输出信号的频率关系表达式,在一定的时钟频率之下,K决定了合成信号的频率,故K被称为频率控制字。

从以上分析不难看出,K也决定了每次累加的相位增量。例如,K=1,其采样相位增量K=2,则K越大,每个时钟周期抽样跨越的相位越大,相位累加器的溢出所需时钟脉冲的个数越少,也即DDS合成信号的频率越高。由此可见,在一定频率的时钟信号作用下,改变每次累加的相位增量,即能改变DDS信号频率。

在得到频率为f0的余弦信号量化的数字的相位序列ψ(n)之后,接着需要实现的是数字相位序列到幅度序列f(n)的转化。根据式(4)和式(5),相位序列ψ(n)和幅度序列f(n)之间有着确定的对应关系。如果将这对应关系固化在一个只读存储器(ROM)中,并且以ψ(n)作为只读存储器的存储单元的地址,而量化后的正弦波形幅度序列f(n)是存储单元的内容。那么,当以相位累加器输出的相位序列ψ(n)对只读存储器寻址时,存储器的输出即为幅度序列f(n)。由f(n)即可构造fs(t),进而得到f(t)实现DDS。

这里需要说明的是,在实际工程中,单位冲激函数是很难实现的,实际抽样往往采用脉冲串函数,其表达式如下

频率合成器 相关文章:

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 直接数字频率合成器的实现设计方案(03-01)

- 基于DDS芯片和集成锁相芯片构成的宽频合成器设计(05-25)

- 基于单片机与FPGA的直接频率数字合成器的设计方案(02-23)