基于VHDL的99小时定时器设计及实现

时间:06-13

来源:互联网

点击:

0引言

传统的定时器硬件连接比较复杂,可靠性差,而且计时时间短,难以满足需要。本设计采用可编程芯片和VHDL语言进行软硬件设计,不但可使硬件大为简化,而且稳定性也有明显提高。由于可编程芯片的频率精度可达到50 MHz,因而计时精度很高。本设计采用逐位设定预置时间,其最长时间设定可长达99小时59分59秒。完全可以满足用户的需要,使用也更为方便。

1系统原理

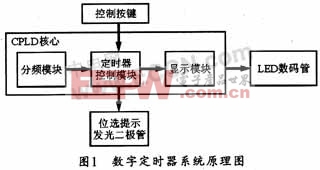

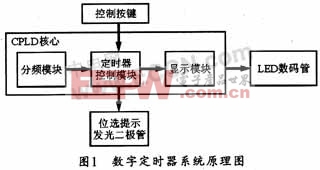

本定时器的核心器件为EP1C6Q240C8芯片。该芯片有选位、置位、启动、复位、倒计时等功能,显示采用2个3位LED数码管,并采用共阴接法,可以动态扫描显示。其系统原理如图1所示。

2 硬件设计

本系统共有两大模块,分别为控制/定时模块和显示模块。其中控制/定时模块包括按键的功能定义和计时的逻辑定义。显示模块则包括片选模块、位扫描模块和数码管译码模块。

设计时可将秒信号输入控制/定时模块,此时系统将输出六个四位BCD码,以分别表示时、分、秒位。在预置数时,计数器可以秒的速度递增,从而实现逐位预置数;而在定时倒计数时,计数器可以秒的速度递减,从而实现倒计时。系统中的位选择器用于对六位进行循环扫描输出,并将扫描输出送到译码器。译码器模块可对输入的四位进行译码,同时在设置数值时用6个LED灯分别指示其所设置的位。

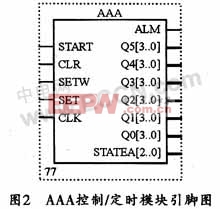

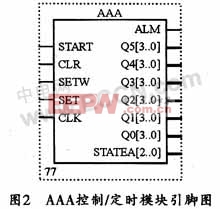

该系统硬件由两部分组成,一部分是EPlC6Q240C8芯片,另一部分是按键,译码器,LED数码管,发光二极管及可编程芯片的支持电路。图2所示是其AAA控制定时模块的引脚排列。其主要功能引脚的定义如下:

Setw(置位键):用于选定定时器所需定时的对应位。发光二极管对应七段数码管设置,当选定对应的位时,相应的发光二极管亮;

Set(置数键):用于设置选定位的具体数值;

Start键:用于设定好时间后启动秒表计时。可通过软件使start按键经过锁存器后进人AAA模块。Start触发后可产生持续的高电平;

ALM(扬声器):可在计时结束时发声报警;

Clr(清零键):用于计时器的清零复位;

七段数码管用于显示定时数字,set模块用控制数码管的扫描频率。

3 主要模块软件程序

图3所示是该定时器的软件系统构成。本软件包括控制/定时模块和显示模块两大部分。

3.1 控制/定时模块

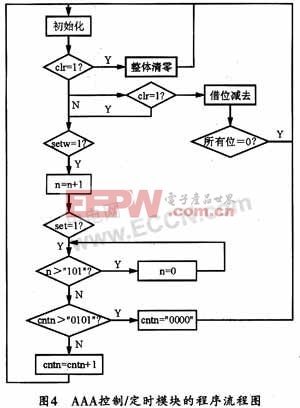

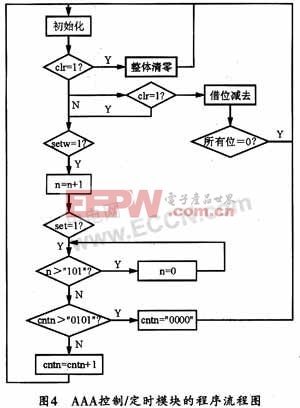

AAA控制/定时模块是该定时器的核心部分,该模块的程序流程图如图4所示。

当START为高电平时,该定时器将进入倒计时阶段。当CLK脉冲上升沿到来时,计数以秒的速度减1,直到计时结束,使ALM位为高电平为止。CLR为复位端,可用来清零,通常采用异步复位方式。SETW用于选位,高电平有效。SET用于对选定的位进行置数,也是高电平有效。ALM输出端将在定时结束时产生高电平。Q0~Q5为四位BCD码输出端口,主要用于显示。

3.2 显示模块

通过XUAN模块可完成BCD码的转化,再经DISP模块译码.然后输出给七段数码管。

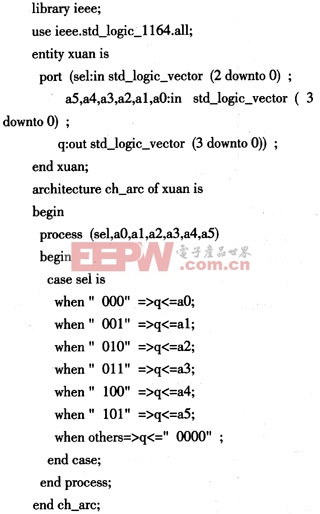

(1)XUAN模块

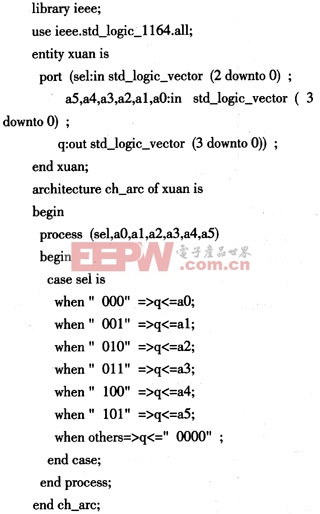

XUAN可产生四位BCD码输入,并从sel端输出。该模块的管脚图如图5所示。其源程序代码如下:

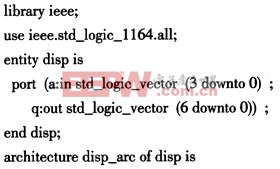

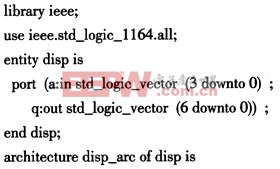

(2)DISP模块

DISP模块主要用于译码,可定义七段数码管显示的数字。其源程序如下:

4 系统仿真及结果

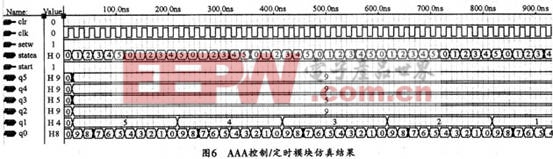

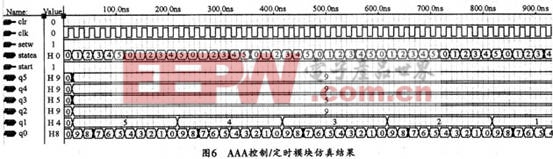

图6所示是对AAA控制/定时模块的仿真结果。由此结果可见,当setw置“1”时,statea位选从0到5循环,分别代表六个数码管的位置。当start置“1”时,q5-q0进行借位减法。q5、q4表示小时,最高可到99小时;q3、q2表示分钟,最高59分钟;q1、q0表示秒,最高为59秒。

5结束语

本设计从总体要求出发,采用模块化设计方法,实现了长达99小时的定时设计。同时采用QuartusⅡ4.0仿真环境进行了仿真。结果证明,本系统可以实现理想的定时操作而且设计体现了人性化,具有较强的实际应用价值。

传统的定时器硬件连接比较复杂,可靠性差,而且计时时间短,难以满足需要。本设计采用可编程芯片和VHDL语言进行软硬件设计,不但可使硬件大为简化,而且稳定性也有明显提高。由于可编程芯片的频率精度可达到50 MHz,因而计时精度很高。本设计采用逐位设定预置时间,其最长时间设定可长达99小时59分59秒。完全可以满足用户的需要,使用也更为方便。

1系统原理

本定时器的核心器件为EP1C6Q240C8芯片。该芯片有选位、置位、启动、复位、倒计时等功能,显示采用2个3位LED数码管,并采用共阴接法,可以动态扫描显示。其系统原理如图1所示。

2 硬件设计

本系统共有两大模块,分别为控制/定时模块和显示模块。其中控制/定时模块包括按键的功能定义和计时的逻辑定义。显示模块则包括片选模块、位扫描模块和数码管译码模块。

设计时可将秒信号输入控制/定时模块,此时系统将输出六个四位BCD码,以分别表示时、分、秒位。在预置数时,计数器可以秒的速度递增,从而实现逐位预置数;而在定时倒计数时,计数器可以秒的速度递减,从而实现倒计时。系统中的位选择器用于对六位进行循环扫描输出,并将扫描输出送到译码器。译码器模块可对输入的四位进行译码,同时在设置数值时用6个LED灯分别指示其所设置的位。

该系统硬件由两部分组成,一部分是EPlC6Q240C8芯片,另一部分是按键,译码器,LED数码管,发光二极管及可编程芯片的支持电路。图2所示是其AAA控制定时模块的引脚排列。其主要功能引脚的定义如下:

Setw(置位键):用于选定定时器所需定时的对应位。发光二极管对应七段数码管设置,当选定对应的位时,相应的发光二极管亮;

Set(置数键):用于设置选定位的具体数值;

Start键:用于设定好时间后启动秒表计时。可通过软件使start按键经过锁存器后进人AAA模块。Start触发后可产生持续的高电平;

ALM(扬声器):可在计时结束时发声报警;

Clr(清零键):用于计时器的清零复位;

七段数码管用于显示定时数字,set模块用控制数码管的扫描频率。

3 主要模块软件程序

图3所示是该定时器的软件系统构成。本软件包括控制/定时模块和显示模块两大部分。

3.1 控制/定时模块

AAA控制/定时模块是该定时器的核心部分,该模块的程序流程图如图4所示。

当START为高电平时,该定时器将进入倒计时阶段。当CLK脉冲上升沿到来时,计数以秒的速度减1,直到计时结束,使ALM位为高电平为止。CLR为复位端,可用来清零,通常采用异步复位方式。SETW用于选位,高电平有效。SET用于对选定的位进行置数,也是高电平有效。ALM输出端将在定时结束时产生高电平。Q0~Q5为四位BCD码输出端口,主要用于显示。

3.2 显示模块

通过XUAN模块可完成BCD码的转化,再经DISP模块译码.然后输出给七段数码管。

(1)XUAN模块

XUAN可产生四位BCD码输入,并从sel端输出。该模块的管脚图如图5所示。其源程序代码如下:

(2)DISP模块

DISP模块主要用于译码,可定义七段数码管显示的数字。其源程序如下:

4 系统仿真及结果

图6所示是对AAA控制/定时模块的仿真结果。由此结果可见,当setw置“1”时,statea位选从0到5循环,分别代表六个数码管的位置。当start置“1”时,q5-q0进行借位减法。q5、q4表示小时,最高可到99小时;q3、q2表示分钟,最高59分钟;q1、q0表示秒,最高为59秒。

5结束语

本设计从总体要求出发,采用模块化设计方法,实现了长达99小时的定时设计。同时采用QuartusⅡ4.0仿真环境进行了仿真。结果证明,本系统可以实现理想的定时操作而且设计体现了人性化,具有较强的实际应用价值。

- VHDL密码控制系统的设计和仿真(11-12)

- 全数字锁相环的设计及分析(03-01)

- 采用CPLD/FPGA的VHDL语言电路优化原理设计(03-18)

- FPGA实现的数字密码锁(07-03)

- 全数字三相晶闸管触发器IP软核设计(06-22)

- 基于DSP和CPLD技术的多路ADC系统的设计与实现(06-11)