VHDL密码控制系统的设计和仿真

随着电子技术和ASIC|0">ASIC技术的发展.数字系统设计向速度快、容量大、体积小、重量轻的趋势发展。目前数字系统设计可直接面向用户需求,根据系统的行为和功能要求,自上而下地逐层完成设计过程:描述、综合、优化、仿真与验证,以及器件生成。该设计过程除系统行为和功能描述外,其他设计几乎都由计算机自动完成,从而实现电子设计自动化(EDA)。这样大大地缩短了系统的设计周期,适应当今品种多、批量小的电子市场要求,提高了产品的竞争能力。由于电子设计自动化是采用硬件描述语言描述硬件电路,所以研究硬件语言及仿真、综合等技术是电子设计自动化的首要任务。本文提出一种利用MAX+plusⅡ开发软件环境和硬件描述语言VHDL的密码控制系统设计方案,并对系统的各个模块进行仿真分析。

2 VHDL语言特点和基本结构

VHDL语言即超高速集成电路硬件描述语言,它是一种用形式化方法描述数字电路和设计数字逻辑系统的语言,特别适合描述复杂的组合逻辑、组运算、状态机和真值表。与传统的门级设计方法相比,VHDL语言具有以下特点:

设计层次高,用于较复杂的运算时能尽快发现问题,缩短产品上市时间,从而成本降低;与工艺无关,独立实现,修改方便,系统描述能力强;可读性好,有利于交流,适合文档保存;VHDL标准、规范并且可移植性强:VHDL类型多且支持用户自定义类型,也支持自顶向下的设计方法和多种电路设计。

VHDL语言程序设计的基本语法结构如下:

密码控制系统包括键盘、控制器和显示器等三部分,如图1所示。

4位密码控制系统设计能实现如下功能:密码验证功能:即用户使用键盘输入4位密码后,按#键确认。如果输入密码正确则输出000l;如果密码错误则输出00000密码更改功能:当用户输入密码正确后,可在此基础上更改密码,即继续输入4位密码,按+键确认,该输入为新密码。如果密码更改成功,则输出1000;作为整体,控制模块有2个输入,即时钟信号和键盘按键信号;两个输出,即键盘扫描信号和结果显示信号,具体如图l所示。该控制模块总共包括分频子模块、键盘扫描子模块、键盘译码子模块、控制子模块以及输出显示子模块,下面分别对各个模块进行编程仿真。

3.1 分频子模块

分频子模块将时钟分频为系统所需频率的时钟信号。通过触发器的级联实现分频电路模块,且级联的触发器级数不同,分频也不同。级数越多频率越低,并按照一定的规律而降低,即频率随级数的增加以分比为l/2的速率降低。本系统设计采用VHDL语言实现分频,其仿真如图2所示。由图2可以看出,CLK-A、CLK-B、VLK-B0和CLK-Bl的频率成倍递减。

3.2 键盘扫描子模块

该模块通过分频子模块提供的分频信号,逐周期扫描键盘的每一行,其信号分别是lll0、110l、lOll和0111,如此循环.即逐周期选中键盘的第一列、第二列、第三列和第四列,实现仿真如图3所示。由图3看出,CLK_SCAN 4位信号中0的位置代表键盘的列位置。

3.3 译码子模块

利用键盘扫描子模块,读取键盘的输入信号,判断哪一个按键被按下,仿真如图4所示。由图4看出,_KEYBOARD是扫描周期,C是键盘按键后的输出信号值;FLAG_NUMB表示按下的是数字键(值为1),OUT_NUMB表示按下的键号,其中15表示功能键(#键和*键);其余数字即为其相应号码键。FLAG FUNC表示按下的是功能键(值为1);OUT FUNC表示其按键值,0100表示*键,000l表示#键,1000表示数字键。

3.4 控制子模块

由于控制子模块无法单独仿真,只能和其他模块一起才能工作,所以无单独仿真图。其功能是获取键盘输入,按规则进行判断并完成相应操作(正确、错误、设置密码、输出结果等)。

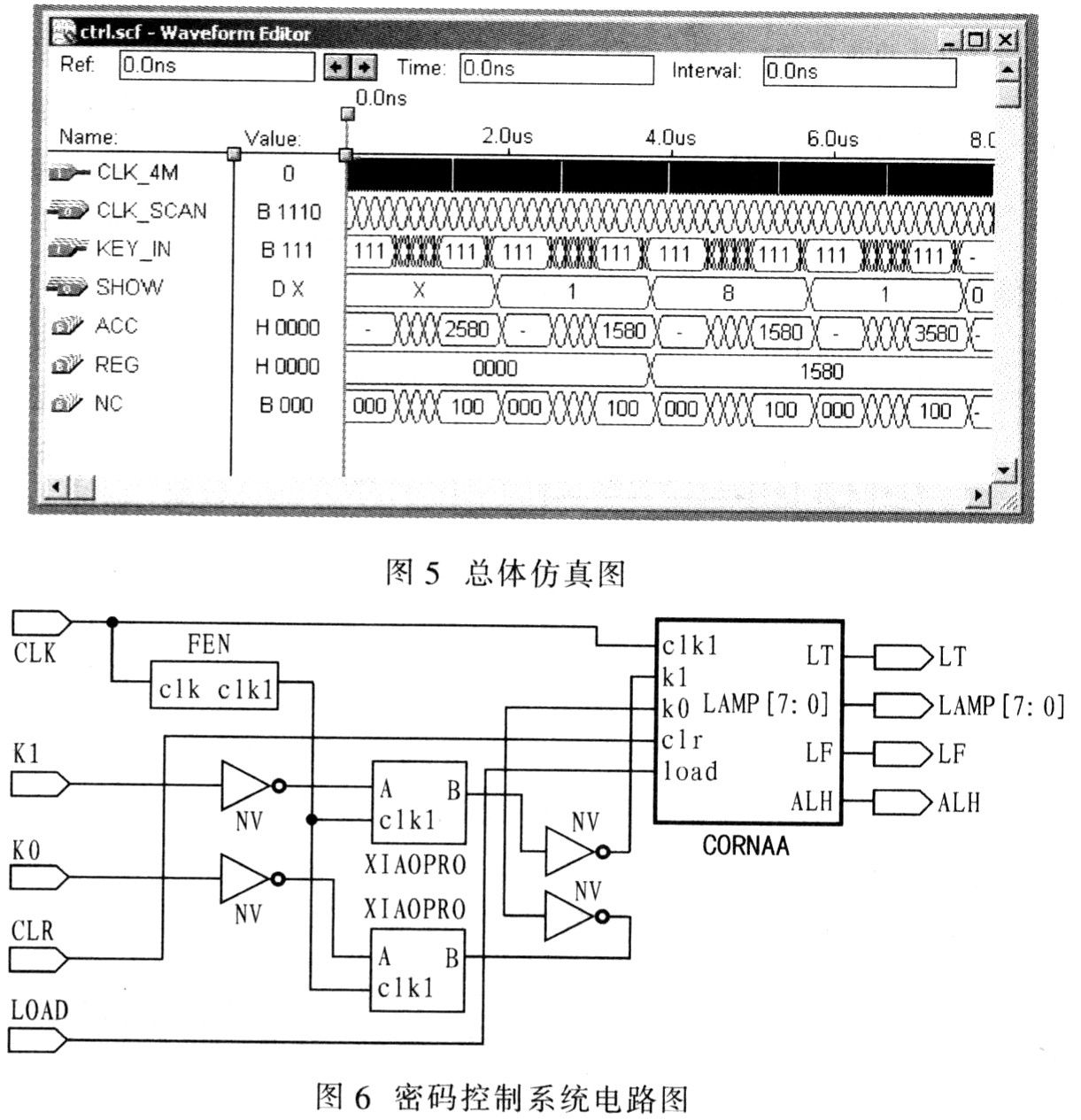

3.5 总体仿真

图5所示为系统总体仿真图,以下说明图5中的信号含义:CLK_SCAN为键盘扫描信号,指出当前扫描键盘的第几行;KEY_IN为键盘按键输入信号,指出当前扫描行的哪一按键被按下:SHOW为判断结果,0表示密码不匹配、1表示密码正确、8表示修改密码成功。ACC为内部移位寄存器。临时存储4个4位二进制数,用于暂存用户输入的密码;REG为内部移位寄存器,临时存储4个4位二进制数,用于保存密码;NC为内部信号,用于表示当前已输入数据数.或者表示用户按数字键的次数。

根据图5所示的总体仿真图,可导出密码控制系统电路,如图6所示。

4 结语

本系统设计是通过自动调用MAX-7000S系列的EPM7128SLC84-6型EPGA器件来实现。并且通过系统总体仿真图能看出设计的密码控制系统完全符合要求。

- 全数字锁相环的设计及分析(03-01)

- 采用CPLD/FPGA的VHDL语言电路优化原理设计(03-18)

- FPGA实现的数字密码锁(07-03)

- 全数字三相晶闸管触发器IP软核设计(06-22)

- 基于DSP和CPLD技术的多路ADC系统的设计与实现(06-11)

- 基于ISP芯片的可编程数字移相器设计(06-23)