FPGA实现的数字密码锁

本文介绍了一种以FPGA为基础的数字密码锁。采用自顶向下的数字系统设计方法,将数字密码锁系统分解为若干子系统,并且进一步细划为若干模块,然后用硬件描述语言VHDL来设计这些模块,同时进行硬件测试。测试结果表明该数字密码锁能够校验10位十进制数字密码,且可以预置密码,设有断电保护装置,解码有效指示等相应功能。

1 功能概述

(1)密码锁的工作时钟由外部晶振提供,时钟频率为50MHz,运算速度高,工作性能稳定。

(2)密码的设置和输入由外接键盘完成,控制电路的安全系数高,操作方便;

(3)密码数字可以由锁的所有者随意设置,并可更改,增强了用户体验。密码修改必须符合预设规则,否则无法修改密码。

(4)开锁时,不限制密码的输入位数(1到10位皆可以),减少了密码被破解的概率(约为10亿分之一的破解率),密码锁的保密能力高。

(5)清除密码键的设定,可以快速清除全部密码,提高了对突发事件的适应能力。

(6)对输入的数字密码既能直接显示,又能转换为星号,防治偷窥,增强保密性。

(7)全部密码输入后,正确时密码锁将开启,显示屏出现:Input Right!指示灯变亮。错误时,显示屏出现:Input Failed!指示灯变灭。

(8)设有断电保护装置,保证电路不会因掉电失去所修改的密码,而回到最初的密码值,增强密码的稳定性。

2 系统结构

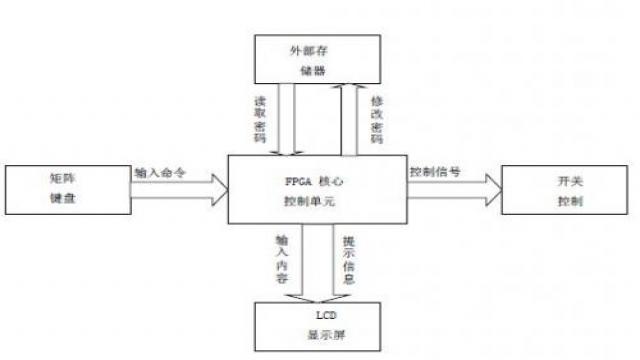

本系统设计主要包括硬件设计和软件设计两部分,均采用模块化设计。其中硬件设计主要包括中央控制模块、微控制器、显示模块、输入模块、外围电路 等内容。软件设计包括状态控制模块,逻辑控制模块,液晶显示驱动模块,EPROM驱动模块,扫描输入模块等构成。系统结构框架图如图1所示。

图1:系统结构框架图

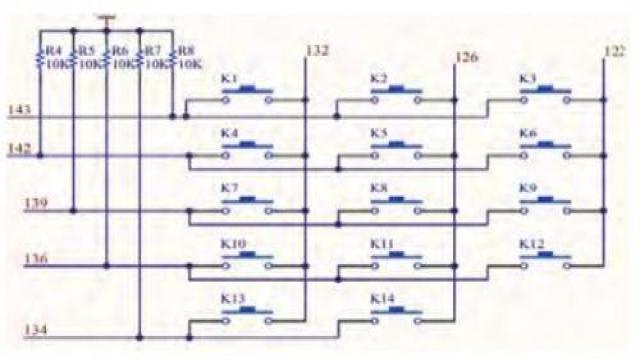

设计采用模块化编程方式,整个程序由液晶LCD1602模块(LCD1602.v)、矩阵键盘模块(Matrix_Keys.v)、存储芯片 AT24C02模块(AT24C_XX.v)和顶层逻辑功能模块(password.v)组成。顶层逻辑功能模块(password.v)调用其他3个模 块完成顶层功能的设计。如图2所示。

图2:矩阵键盘原理图

3 底层设计

3.1 输入模块

由于键盘按键数量较多,为了减少I/O口的占用,本设计将按键排列成矩阵形式。在矩阵式键盘中,每条水平线和垂直线在交叉处不直接连通,而是通 过一个按键加以连接。这样,8个端口就可以构成3*5=15个按键,实际上我们只用14个按键就足以解决密码问题,比之直接将端口线用于键盘多出了一倍, 而且线数越多,区别越明显,比如再多加一条线就可以构成20键的键盘,而直接用端口线则只能多出一键(9键)。故在需要的键数比较多时,采用矩阵法来做键 盘是更合理的方案。

3.2显示模块与外围电路

本设计选用了LCD1602作为显示模块的核心,可以方便地显示所需的数字和提示语,具有界面人性化、功耗低、速度快、节约控制器资源等优点。外围电路主要是一个受控制器控制的LED,由于表示锁的开启与关闭。

3.3存储模块

本设计使用存储芯片AT24C02作为密码的外部存储器。二线制串行EEPROM—24C02是低工作电压的2K位串行电可擦除只读存储器,内 部组织为256个字节,每个字节8位,该芯片被广泛应用于低电压及低功耗的工商业领域。设计使用I2C协议实现控制器与存储器的联结,实现密码保存,并保 证密码不会因断电丢失。

4 工作方式

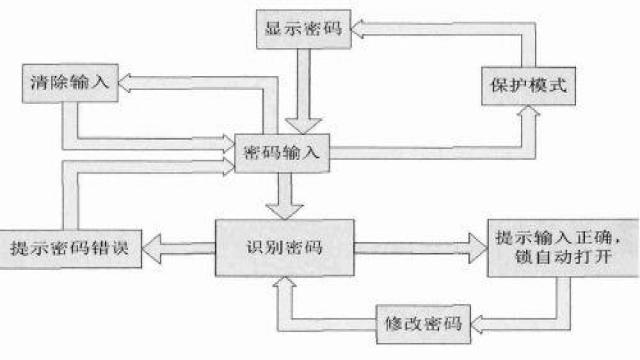

本系统利用上述系统模块作为硬件基础,使用VHDL语言编写程序,实现了五大主要功能:

(1)确认密码:通过扫描矩阵键盘,判断用户输入内容,将键入的数码与密码存储器中的密码进行比较,判断密码的正误,并控制密码锁的开关;

(2)清除密码:输入密码过程中发生按键失误,可以通过选择清除键清除当前全部的密码,方便重新输入;

(3)密码保护:通过显示切换键,可以切换显示模式。在显示数字模式下,显示屏即显示输入的数字,方便用户操作;在保护模式下,显示的密码用"*"表示,防止外界偷窥,提高安全性能;

(4)修改密码:当密码锁处于打开状态时,默认识别当前用户为锁的持有者,允许修改密码。但修改密码必须符合密码锁内设的"潜在规则",否则无法完成修改,防止密码锁被破坏;

(5)断电保护:设置电路保护结构,保证电路不会因掉电失去所修改的密码,而回到最初的密码值。

其工作流程图如图3.

图3:工作流程图

5 仿真与调试

在设计过程中,首先针对各个模块,使用Quartus II等软件进行仿真,然后将程序烧录进行硬件调试。最后,将整个系统程序进行全编译,进行整个系统的软件仿真,仿真通过后进行整个系统的硬件调。

6

FPGA 仿真 AT24C02 串行 VHDL 控制器 相关文章:

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)