基于压控振荡器(VCO)的高性能锁相环(PLL)设计

时间:11-01

来源:互联网

点击:

集成VCO的宽带宽PLL

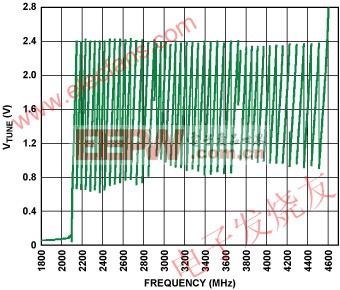

另外可以用完全集成的高性能PLL,例如图2所示的ADF4350等,代替有源滤波器与高压VCO组合。这种情况下,VCO集成在芯片内。采用多频段VCO方法可以避免上述权衡考虑宽调谐范围与低相位噪声的问题。ADF4350片内集成三个独立的VCO,每个VCO均有16个重叠子频段,因而共有48个子频段。每次更新频率时,就会启动自动校准程序,以选择合适的VCO子频段。这真正体现出从分立式VCO设计转向硅解决方案的优势:在极小的面积上实现非常高的集成度,从而使设计更加灵活。例如,ADF4350同时集成了可编程输出分频器级,可以覆盖从137.5 MHz至4.4 GHz的频率,这对于希望多种频率和标准均采用同一设计的无线电设计师极具吸引力。

ADF4350采用5 mm2 LFCSP封装,而标准VCO封装为12.7 mm2。同时性能水平也接近分立设计;相位噪声在100 kHz偏移时为–114 dBc/Hz,在1 MHz偏移时为–134 dBc/Hz。(返回图2)

图6. ADF4350 VCO中48个不同频段的电压与频率关系图

- 一种大电压输出摆幅低电流失配电荷泵的设计(04-22)

- 压控振荡器(VCO)的设计(03-25)

- 增加RC压控振荡器的频率区间(03-14)

- 基于微波谐振腔的葡萄糖溶液浓度测量系统(02-11)

- 可调控VCOM可产生精确参考电压(07-16)

- PLL-VCO制作方法介绍(05-04)