边缘图像连通区域标记的算法研究和SoPC实现

2 区域标记及合并的SoPC实现

本文以FPGA为核心,利用SoPC技术,实现了对320×240图像的8方向生长连通区域标记。系统使用FPGA逻辑硬件进行边缘检测[3],使用NiosII软核处理器进行连通区域标记,用Avalon总线将两者结合起来,实现了硬件加速,软硬件协同工作,既提高了实时性又保证了灵活性。

2.1 SoPC系统的结构设计

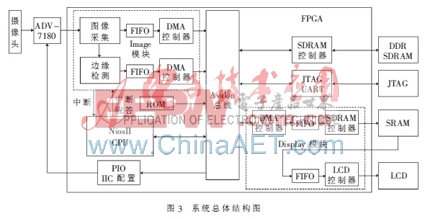

系统结构图如图3所示,主要模块的功能简述如下:

(1)NiosII CPU模块。该模块是整个系统运算和调度的中心,完成系统工作流程的控制;图像处理中区域标记和区域合并算法的实现;图形用户接口(GUI)的实现。

(2)Image模块。图像采集部分负责按照320×240大小采集摄像头的数据,由DMA控制器通过Avalon总线将原始图像数据存储到DDR SDRAM中。边缘检测部分同步地将原始图像数据边缘化,生成边缘图像数据,并通过DMA控制器和Avalon总线存储到DDR SDRAM中。

(3)Display模块。负责驱动LCD液晶显示屏显示原始图像、标记图像以及处理信息。

2.2 区域标记及合并的算法实现

图像处理过程分为连通区域标记、区域合并和区域排序三步。

(1)连通区域标记:按照改进后的8方向邻域生长算法进行连通区域标记,为每个连通区分配一个链表数组元素,用链表记录该连通区的目标点和端点。

(2)区域合并:逐个比较任意两个连通区域的端点链表,在大尺度范围内(本文采用9×9范围),若其中有相邻的端点,则合并这两个连通区。

(3)区域排序:按照目标点的个数,从大到小对合并后的连通区域排序,取前N个目标点数大于X的连通区域作为后续特征提取的对象(本文N的最大取值为10,X取值20),其余的视为干扰去掉。取形状较大的N个连通区进行下一步的特征提取,可以节省处理时间。

3 实验结果及分析

本文使用Altera公司的高性价比CycloneIII系列的FPGA EP3C25F324C8。SoPC系统共用逻辑单元8916/24624(36%),寄存器5 415个,引脚101个,片内SRAM位数421 248/608 256(69%),内置乘法器4个,PLL锁相环1个。系统时钟为100 MHz,NiosII软核处理器的性能为113 DMIPS。

实验结果如图4所示。图4(a)为实验用开发板和摄像头,图4(b)、(c)、(d)是不同图像在LCD液晶屏上显示的实验结果。显示分为三部分:左侧上部为原始灰度图像,大小为320×240;左侧下部为标记图像(不同区域由不同颜色显示),大小为320×240;右侧为处理信息,大小为480×480。处理信息包括:Connection Num为连通区域个数;Merge Num为合并后的区域数;Region Num为排序后的区域数;Process Time为图像处理时间,单位为ms。

实验结果表明,本文算法得出的标记图像结果正确、边缘清晰、去掉了杂点、提高了区域的连通性。在SoPC系统上实现时,对复杂图像的处理速度约30帧/s,满足了实时性要求。

本文在SoPC系统中,将提出的基于目标像素邻域的8方向生长区域标记算法和基于边缘端点的区域合并算法成功地予以实现。实验结果表明了算法的有效性和实时性。基于SoPC技术的图像处理系统,软硬件协同工作,提高了系统的并行性和灵活性,便携性好,成本低。

参考文献

[1] HE Lifeng,CHAO Yuyan,SUZUKI K.Fast connected-component labeling[J].Pattern Recognition,2009,42(9):1977-1987.

[2] HU Qingmao,QIAN Guoyu.Fast connected-component labelling in three-dimensional binary images based on iterative recursion[J].Computer Vision and Image Understanding,2005,99(3):414-434.

[3] 谢昭莉,白颖杰.Prewitt图像边缘检测及边缘细化的FPGA实现[J].电子技术应用,2010,36(6):39-42.

- 基于Nios II的数字音频录放系统的设计(01-08)

- 基于SOPC技术的交通事故自动处理设备(10-05)

- SOPC设计中自定义IP的开发(02-18)

- 基于SOPC技术的软件无线电系统研究(04-07)

- 基于DSP的彩色TFT-LCD数字图像显示技术研究(05-05)

- 3D集成电路将如何同时实现?(04-09)