一种模/数混合型FIR噪声滤波器设计

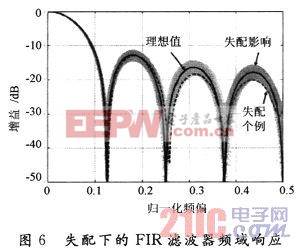

对于其他纯模拟的量化噪声抑制技术,比如采用数/模转换器补偿量化误差的方法,失配将造成整个频带上噪声抑制效果的恶化。从图6可以看到,混合型FIR噪声滤除技术中,失配主要影响传递函数的零点位置。在远离零点的频偏处,滤波器增益的变化在±3 dB以内;而在预期的零点位置处,即便有失配存在,仍然能保证有至少25 dB的抑制,这通常已经足以把量化噪声降低到不再影响整体性能的水平。此外,从图中虚线给出的不失一般性的个例可以看到,尽管失配使得在一些频偏处的噪声抑制程度不如预期值,但也使得在其他频偏处的噪声抑制要优于预期值。这个特性进一步使得量化噪声的总体改善对失配不敏感。

3 并行支路间的准同步

传统△-∑锁相环或△-∑延时锁定环中只有一个鉴相器,其输入端的参考时钟和环路反馈回来的信号时钟之间在锁定后只存在由式(4)给出的瞬时相位误差,这决定了电荷泵的开启时间和对应的噪声注入。而在采用混合型FIR噪声滤除技术的结构中,存在并行多支路鉴相器。它们一方面共享同一个参考时钟,另一方面则是由各自对应的分频器或相位选择器产生各自的信号时钟,因此存在是否需要对这些信号时钟加以同步的问题。

支路间处于异步状态时将造成的问题如图7所示。

为不失一般性,此处假设要实现一个简单的2抽头FIR滤波器,其传递函数为(1+z-1)/2,因此环路中将需要用到2个支路的鉴相器。如图7所示,在环路建立后,参考时钟沿将被锁定在2个信号时钟沿的中间。因此,如果两个信号时钟沿的相位差为△φ,则对于每个鉴相器而言,输入端的瞬时相位误差比原来增加了△φ/2。此外,为了保持环路的锁定,2个电荷泵支路需要在每个鉴相周期内交替充放电。支路间的相位差△φ越大,也就意味着电荷泵开启时阊以及噪声注入时间越长,从而严重恶化带内相位噪声以及参考杂散性能。另一方面,支路间异步引入的附加相位偏移还将影响所要实现的混合型FIR滤波器的传递函数。

为了避免这些性能上的恶化,混合型FIR噪声滤除技术在电路实现上需要保证并行支路间处于准同步状态,即各信号时钟的相位差应满足:

式中:φi和φj分别为第i和j路信号相位;Ni和Nj为支路对应的控制字;φstep为相位量化步长。可见,这里的“准同步”包含2个含义:一方面,由于各支路的信号时钟受控于不同的控制字,因此不可能实现零相位差的完全同步;另一方面,各支路信号时钟的相位差应当仅由量化控制字的差异引起,无任何附加相位差。

图8是4电平量化下支路准同步后的时钟信号示例。各支路信号时钟在同样的4个备选相位间切换,从而对于任何一个支路而言,其工作状态都和传统结构完全一致,这就实现了真正意义上并行操作和离散时间域的信号合成。

就电荷泵本身而言,由于其总电流与传统结构一致,这使得所用的有源器件总体尺寸保持不变,从而贡献的噪声也就不变。惟一的差别是多输入电荷泵中需要多用若干个开关管,其带来的噪声恶化几乎可以忽略。

4 电荷泵非线性的改善

在△-∑锁相环或△-∑延时锁定环里,电荷泵的非线性将造成高频量化噪声被折叠到低频,从而影响带内相位噪声性能。采用了混合型FIR噪声滤除技术后,由于环路中并行的鉴相器和电荷泵支路是由△-∑调制器的输出经过不同时钟周期延时后依次控制的,因此会对各支路受数字控制的相位误差有类似“桶形移位”的效果。如图9所示,尽管该结构没有像模/数转换器设计中的桶形移位技术一样存在控制字的卷绕,但多支路的并行工作配合依序的控制,使得所有相位误差电荷在电荷泵中合成后,各支路数控相位到模拟域电荷的非线性映射可以得到平均和改善。

式中:ICP为电荷泵电流;△ICP为失配电流;△V为电荷泵输出电压改变量。

可以看出,混合型FIR滤波器在实现预期噪声整形的同时,也减小了由于电荷泵非线性造成带内噪声的恶化。作为一个特例,尽管各支路存在如图9所示的非线性,但当它们叠加之后恰好是线性特性时,该结构将能完全消除每个支路非线性的影响。但是由于这种巧合在实际电路中几乎不存在,因此通常不能实现彻底的线性化改善,在设计中仍然需要注意结合其他一些提高线性度的考虑。

5 额外的开销

从图1给出实现混合型FIR噪声滤波的电路结构可以看出,该技术相比传统结构需要额外的硬件开销,包括一个多输入电荷泵、多个鉴相器,以及用于实现调制器输出延时的寄存器链。此外,由于送至鉴相器的环路反馈信号在锁相环和延时锁定环中分别由分频器和相位选择器或插值器得到,这意味着这些模块也需要有多个。

对于多输入电荷泵,由于其总电流必须和传统结构中的电荷泵一致,以维持环路原始动态特性,因此电路中只是存在更多的开关管,几乎没有额外的面积和功耗的开销。

对于其他模块,由于它们都属于单端数字电路,因此面积和功耗可以随着CMOS工艺的进步得到成比例的改善。这也意味着如果采用先进的工艺,则可以在较低的代价下实现更多抽头数的FIR滤波器,以达到更好的噪声抑制效果。

然而由于分频器消耗的电流随着工作频率的提高而急剧增加,这使得在高频无线应用中采用混合型FIR噪声滤除技术时存在巨大的功耗开销。为了解决这个问题,在分频器设计上可以遵照移相的方法来实现等效分频,从而使并行支路问可以共用最耗电流的前级预分频器,以降低总功耗。

6 结语

本文提出的一种混合型FIR噪声滤波技术,其基本电路结构是:将△-∑调制器的输出经过一个寄存器链加以延时,从中选取若干抽头去控制并行的多支路分频器或相位选择器,并各自经过鉴相器判别相位差,最后各支路对应的误差电荷在一个多输入电荷泵中加以合成,由此可以在不改变环路动态特性的同时,实现对量化噪声的等效FIR滤波。由于这种技术基于离散时间域工作,因此继承了现有数字FIR噪声滤除技术对PVT变化以及模拟失配不敏感的优点;同时又结合模拟域的电荷合成解决了数字FIR滤波器的噪声增益问题;而其并行多支路工作配合依序控制的结构特点又带来降低对电荷泵线性度要求的额外好处。此外,相比其他纯模拟的量化噪声抑制技术,该技术也有硬件成本上的优势。

- 用频率采样法设计FIR滤波器(10-07)

- 高阶FIR滤波器的计算机设计与FPGA实现(03-13)

- FIR结构IQ串行处理RRC滤波器(04-18)

- 优化FIR数字滤波器的FPGA实现(04-18)

- 基于Matlab的FIR数字滤波器设计(10-07)

- 详解FIR滤波器和IIR滤波器的区别(04-04)