高阶FIR滤波器的计算机设计与FPGA实现

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR滤波器获得了更广泛的应用。FIR滤波器有多种设计和实现方法,最为常用的是基于分布式算法的FIR滤波器设计。该法利用构造查找表,流水线操作完成滤波过程,极大地提高了系统的处理效率。然而,查找表所要求的系统存储器容量随滤波器的阶数成指数上涨。本文基于工程实际出发,在信号处理速率要求不高且滤波器阶数较高的情况下,提出了一种基于LPM参数化宏功能模块的FIR滤波器设计方法,具有一定的工程实用价值。

1 FIR滤波器的原理与设计方法

1.1 FIR滤波器的原理

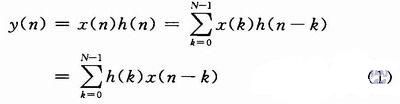

FIR滤波器的数学表达式为:

式中:N为FIR滤波器的抽头数;x(n)为第n时刻的输入样本;h(k)为FIR滤波器第k级抽头系数。

直接型FIR滤波器结构如图1所示。

由图1可见,FIR的滤波过程就是一个信号逐级延迟的过程,将各级的延迟输出加权累加,即得到FIR的输出,其中最主要的算法是乘累加运算。由于FIR每完成一次滤波过程就需要进行N次乘法和N-1次加法操作,所以FIR滤波的运算量完全依赖于N的大小。

1.2 分布式FIR滤波器设计

分布式算法(Distributed Arithmetic,DA)早在1973年就已经被Croisier提出,直到现场可编程门阵列(Field Programmable Gate Ar-ray,FPGA)的查找表(Look Up Table,LUT)结构出现,这种算法才重新受到重视,其主要原理如下。

为了分析简单,将FIR滤波器的表达式(1)改写为:

可见,分布式算法是一种以实现"乘-加"单元为目的的优化解决方案。利用一个查找表(LUT)实现映射,即用一个2k字宽(即2k行),预先编好程序中LUT接收到的一个K位输入向量Xb=[X0b,X1b,…,X(k-1)b]的映射,经查找表的查找后直接输出部分积。然而,由上述可知,查找表字宽为2k,如果滤波器的抽头系数过多,则查找表的规模随抽头系数的增加成指数级增长,这将使LUT的规模十分庞大。为了减小规模,可以利用部分表计算法,即将一个大的查找表化分为几个小的查找表,然后再将结果相加。

1.3 基于LPM参数化宏功能模块的FIR滤波器设计

由1.2节可见,分布式算法极大地减少了硬件电路规模,很容易实现流水线技术,不仅使电路的执行速度得以提高,使得信号的处理效率大幅度提高。然而,当系统所要求的处理速度不高时,可利用QuartusⅡ中的LPM参数化宏功能模块来设计FIR滤波器;当滤波器系数较大时,该法不需要像分布式算法那样构造庞大的查找表或多个小的查找表。

1.3.1 LPM参数化功能模块简述

LPM是参数可设置模块库(Library of Parameterized Modules)的英文缩写,设计者可以根据实际电路的需要,选择LPM库中的适当模块,并为其设定适当的参数,以满足设计的要求。常用的LPM宏功能模块有诸如累加器、加法器和乘法器等的算术组件;多路复用器和LPM门函数还有诸如和I/O组件、存储器编译器等等的门电路,用户可以根据自身需要查阅相关的资料。本文正是利用其中的乘法器和累加器来完成FIR滤波器的设计。

1.3.2 FIR滤波器的设计

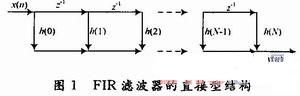

在QuartusⅡ中,利用"Megawizard"向导生成所需的模块,其界面如图2所示。

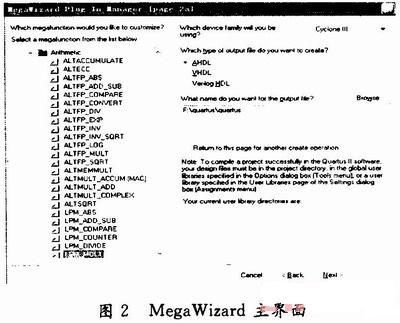

选择图中左侧Arithmetic中的LPM_MULT得到图3的界面,根据技术指标选择合适的参数,即可生成乘法器模块,按其向导,完成乘法器参数的设置(如乘数的位数,是否有符号数相乘等)。加法器模块的构造类似,不再详述。

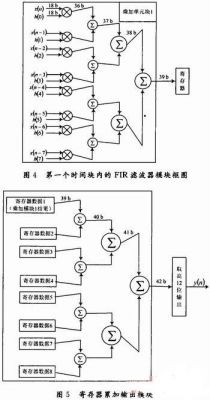

以本文设计的FIR滤波器为例(后面详述),输入信号的速率为2 MHz(周期为500 ns),滤波器的阶数为64阶,由此构造了8个乘法器(最多可以构造25个),分8次完成所有的乘法。相对分布式算法的流水速度而言,构造的乘法器完成一次乘法需要20 ns,相对耗时长一点,但是完成8次乘法也只需8×20=160 ns,小于输入信号一个周期的时间,因此满足设计需求。将输入数据的一个周期平均分为8个时间块,每个时间内的FIR滤波设计模块的框图如图4所示。

其他7个时间块内的FIR滤波器模块同图4,所不同的是参与乘法运算的信号输入数据和滤波器抽头系数不同,分别从x(n-8)到x(n-63)和h(8)到h(63)。待8个乘加模块的结果均送入寄存器后,再在最后一个时间块内完成累加得到最终的输出(相对乘法运算而言,完成累加的时间可以忽略),其实现框图如图5。

结合图4和图5,可全部完成基于LPM参数化宏功能模块的FIR滤波器设计。由两图可以发现,有多个全加器,且输入数据的位数(bit数)不同,只要调节LPM宏功能模块的参数即可方便地完成设计,输出数据y(n)的位数则根据工程需要取最终累加结果的高12位。取高12位带来的误差为(最高位为符号位,不予数值考虑),这是可以接受的误差。

- 用频率采样法设计FIR滤波器(10-07)

- FIR结构IQ串行处理RRC滤波器(04-18)

- 优化FIR数字滤波器的FPGA实现(04-18)

- 基于Matlab的FIR数字滤波器设计(10-07)

- 详解FIR滤波器和IIR滤波器的区别(04-04)

- GreenFire系统:智能电网的核心(08-25)