FIR结构IQ串行处理RRC滤波器

0 引言

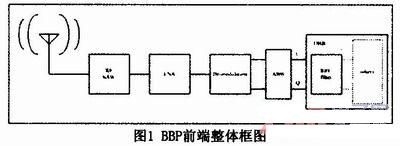

由3GPP WCDMA协议25.213可知,下行调制分为QPSK与16QAM两种方法,但是经过扰码加扰与信道码处理后均达到3.84Mbps,即达到3.84M的码片速率。基带处理器中采用16倍码片速率,61.44MHz进行采样。在基带数据发送与接收时使用RC成形滤波器,考虑到减小码间串扰与接收滤波器匹配的关系,在发送与接收端均使用RRC(根升余弦)滤波器。整体流程太致如图1所示。

射频接收部分只是简单描述了一下,图中ABB为模拟基带,主要有ADC、∑△调制、降采样滤波器组成,当然还包括语音编解码等基本功能,DBB为数字基带部分。两者结合成为基带处理器。通常由ABB送入后端系统为IQ并行两路数据,当基带信号没有携带其他带通信号的干扰时,或者下变频时没有非常大的频偏,这样通常进行滤波时使用两套相同滤波系数的滤波器,这也意味着两套相同的乘法器与加法器,当滤波器阶数较高时,会造成资源的大量消耗,增加ASIC的面积,故本文利用了4倍速采样的样本,复用同一套乘加器,有效节省了资源。

1 RRC滤波器

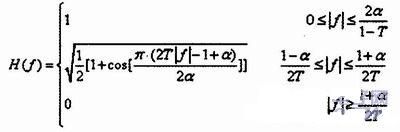

RC滤波器可以减小码间串扰,同时也是信号成形滤波器。其能有效地减小信号带宽,抑制码间串扰,并且考虑到在接收端要使用匹配滤波,所以在信号发送与接收端均采用RRC滤波。其频域响应如下:

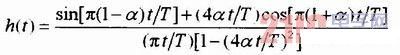

通过对如上频域响应使用Fourier逆变换,我们可以得到其时域冲击响应如下:

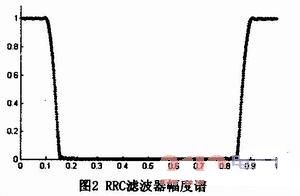

考虑IIR与FIR等基本滤波器结构,由于相位的线性特性对实时通信具有重要的意义,并且RRC滤波器处于整个数字基带处理器的前端,其滤波性能,由量化效应导致的稳定性问题等,对后续系统有一定影响,故我们采用FIR结构,滤波器采用65阶,因为阶数并未超过256,且处理信号为基带信号,故RRC是一个低通滤波器,因此采用偶对称系数结构FIR滤波器。通过Matlab仿真我们可以得到如下的RRC滤波器幅度谱:

图中采用了f-sample=15.36MHz的采样频率对h(t)进行了采样,由冲击响应不变法形成了数字频率域上FIR结构滤波器的冲击响应系数,即FIR滤波系数。在频域上每隔10kHz对幅度函数进行采样,横轴采用归一化频率表示,由于采样是时域采样,所以频域上产生了周期性延拓。但是由此图可以看出,幅度谱还是基本能够满足成型滤波需求,又由于采取了FIR结构,故其系统函数可表示为

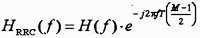

其中H(f)为如上RRC滤波器的频率域上的形势,为FIR引入的相位延迟。并且由于是奇数阶FIR滤波器,系数呈现偶对称的关系,滤波器系数满足如下条件:

上文简要介绍了基于FIR结构RRC滤波器的基本原理与特性,下文重点描述在WCDMA基带芯片数字前端中如何串行模拟基带输送的并行IQ路数据。

2 IQ串行RRC滤波器

对于下行信号,按照25.213(release6)协议规定码片速率为3.84Mbps,考虑到采样定理与模拟基带普遍采用的调制方式,在模拟基带处使用16倍码片速率采样,即ABB采用61.44MHz频率主时钟采样信号,产生4bit的PDM码。其后DBB也采用16倍速对数据进行处理。当然RRC端输入数据已经经过降采样滤波器处理,采样数据降低为15.36MHz,即4倍速码片速率。但由于射频前段均采用IQ双通道结构,所以此时形成了I路与Q路两路并行数据流,因此需要两个RRC滤波器并行处理数据,因此使得系统资源大量浪费。所以本文进一步利用了4倍速码片速率并行IQ数据,添加了一个由计数器形成的控制部分,改变普通FIR滤波结构,复用了RRC的资源,同时完成了IQ两路数据流的处理。

2.1 IQ并串转换

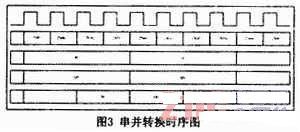

首先将两路并行IQ数据降采样后进行并串转换,主时钟采用16倍速码片速率,为61.44MHz。转换控制由计数器完成,计数器为2bit,在高位为1时刻采样I路,在高位为0时刻采样Q路,整个转换过程如图3所示。

2.2 串行处理滤波器结构

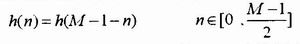

其后采用FIR结构实现RRC滤波器,其中数据输入端使用IQ路串行输入,即上一节中的串行数据。由于奇数阶M=65FIR滤波器的时域特性,其冲击响应满足如下条件:

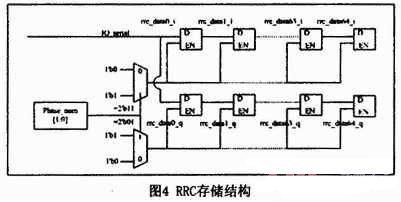

因此对于不同部分的存储单元可以使用相同的加法单元,在下面的复用乘加器中可以设计复用结构。这里描述FIR数据存储的结构,其中由计数器Phase_num控制数据在滤波器存储单元中的流动。高位为1时存储I路数据,高位为0时存储Q路数据。数据存储单元无法复用,因为这是滤波必需的。但是乘加器则可以通过如下小节中描述的方式复用。

2.3 复用乘加器结构

同样,依靠计数器控制,我们可以复用同一套乘加资源,但是存储单元依然和使用两套FIR结构相同,这也体现了ASIC设计的本质。从图5中我们就可以发现乘加器的输入也由同一个计数器控制,计数器高位为1时,计算I路数据滤波结果,计数器高位为0时,计算Q路滤波结果,随后经过两级触发器

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 视频有源滤波器 (11-26)

- 通用和低噪声的有源滤波器提供达10MHz的可重复性能(01-05)

- 直流耦合视频放大器/滤波器的视频信号电平转换(07-03)

- 开关电容梳状滤波器幅频特性的深入分析(06-05)

- 在高温超导滤波器后级的低温低噪声放大器的设计和调试方法(06-01)