FIR结构IQ串行处理RRC滤波器

时间:04-18

来源:陈泳恩 宋志豪同济大学

点击:

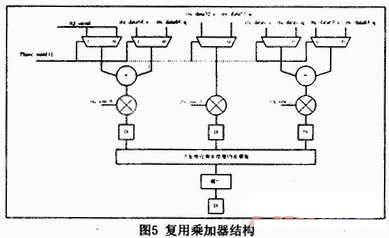

缓存,在输出端形成串行IQ路数据,如此结构就节省了两套FIR滤波器中的乘法器与加法器的结构,当FIR阶数较高时就有效地节省了资源,但是这是有前提的,即射频部分在下变频时并没有残留太大的频偏,也就是说当基带信号并不是很理想时,或者有一个带通信号对其进行干扰时,IQ路RRC滤波器是不一样的,那么此时滤波系数就是不同的,则不可避免地需要两套RRC结构。

3 结论

本文通过改变通常FIR处理结构,有效地节省了资源,只使用了一套乘加器,一套FIR滤波器结构,就完成了两套FIR滤波器的功能,虽然数据存储单元与两套FIR相比并未减少,但是有效地减少了乘加资源的使用,提高了运算效率,节省了ASIC芯片的面积。当RRC滤波器阶数较高时,效果更为明显。

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 视频有源滤波器 (11-26)

- 通用和低噪声的有源滤波器提供达10MHz的可重复性能(01-05)

- 直流耦合视频放大器/滤波器的视频信号电平转换(07-03)

- 开关电容梳状滤波器幅频特性的深入分析(06-05)

- 在高温超导滤波器后级的低温低噪声放大器的设计和调试方法(06-01)