针对DDR2-800和DDR3的PCB信号完整性设计

MM组里,对于ADDR/CMD/CNTRL所采用的拓扑结构里,带有少的短线菊花链拓扑结构和树形拓扑结构是适用的。

10. 案例

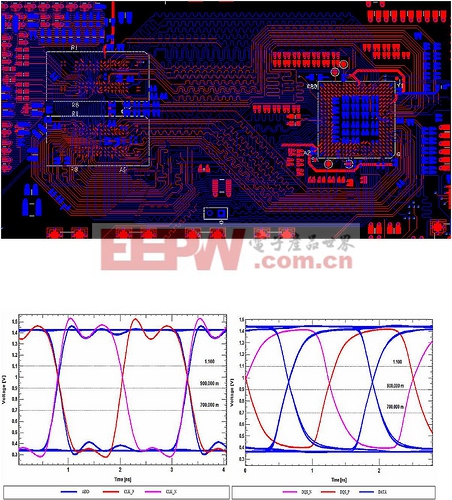

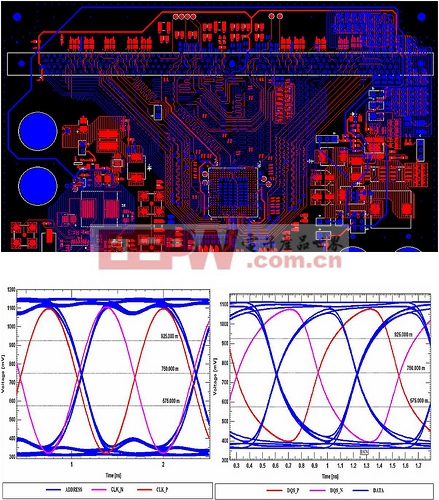

上面所介绍的相关规则,在DDR2 PCB、DDR3 PCB和DDR3-DIMM PCB里,都已经得到普遍的应用。在下面的案例中,我们采用MOSAID公司的控制器,它提供了对DDR2和DDR3的操作功能。在SI仿真方面,采用了 IBIS模型,其存储器的模型来自MICRON Technolgy,Inc,对于DDR3 SDRAM的模型提供了1333 Mbps的速率。在这里,数据是操作是在1600 Mbps下的。对于不带缓存(unbuffered)的DIMM(MT_DDR3_0542cc)EBD模型是来自Micron Technology,下面所有的波形都是采用通常的测试方法,且是在SDRAM die级进行计算和仿真的。图2所示的6层板里,只在TOP和BOTTOM层进行了布线,存储器由两片的SDRAM以菊花链的方式所构成。而在DIMM的案例里,只有一个不带缓存的DIMM被使用。图9-11是对TOP/BOTTOM层布线的一个闪照图和信号完整性仿真图。

图9: 只有在TOP和BOTTOM层走线的DDR3的仿真波形

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络,其时钟频率在800 MHz,数据通信率为1600Mbps)

图10: 只有在TOP和BOTTOM层走线的DDR2的仿真波形

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络,其时钟频率在400 MHz,数据通信率为800Mbps)

图11: 只有在TOP和BOTTOM层走线的DDR3-DIMM的仿真波形

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络)

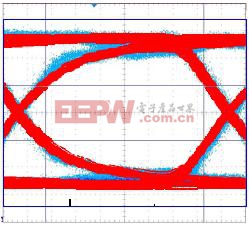

最好,图12显示了两个经过比较过的数据信号眼图,一个是仿真的结果,而另一个是实际测量的。在上面的所有案例里,波形的完整性的完美程度都是令人兴奋的。

图12: 800 Mbps DDR2的数据信号仿真眼图(红) 和 实测眼图 (蓝)

11. 结论

本文,针对DDR2/DDR3的设计,SI和PI的各种相关因素都做了全面的介绍。对于在4层板里设计800 Mbps的DDR2和DDR3是可行的,但是对于DDR3-1600 Mbps是具有很大的挑战性。

- 先进高速传输接口及高速DDR存储器技术(02-10)

- 电源设计小贴士 41:DDR内存电源(11-21)

- TI推出业内首个完全集成的DDR存储器电源解决方案(09-12)

- 8位1.0GSPS ADC芯片MXT2001原理与应用(11-07)

- 用Xilinx FPGA实现DDR SDRAM控制器(11-30)

- 基于IDDR的亚稳态问题解决方案介绍(08-18)