针对DDR2-800和DDR3的PCB信号完整性设计

种方法去解决它。一种方法是,只需要在 EDA工具里进行精确的时延匹配计算,然后控制走线的长度就可以了。而另一种方法是在可接受的范围内,减少不匹配度。

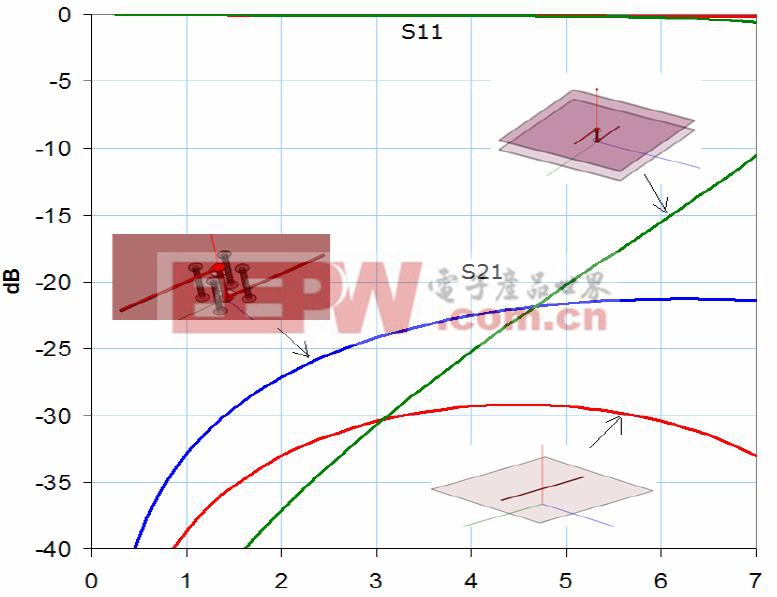

对于trombone线,时延的不对等可以通过增大L3的长度而降低,因为并行线间会存在耦合,其详细的结果,可以通过SigXP仿真清楚的看出,如图 5,L3(图中的S)长度的不同,其结果会有不同的时延,尽可能的加长S的长度,则可以更好的降低时延的不对等。对于微带线来说,L3大于7倍的走线到地的距离是必须的。

图5: 针对trombone的仿真电路和仿真波形

trombone线的时延是受到其并行走线之间的耦合而影响,一种在不需要提高其间距的情况下,并且能降低耦合的程度的方法是采用saw tooth线。显然,saw tooth线比trombone线具有更好的效果,但是,它需要更多的空间。由于各种可能造成时延不同的原因,所以,在实际的设计时,要借助于CAD工具进行严格的计算,从而控制走线的时延匹配。

考虑到在图2中6层板上的过孔的因素,当一个地过孔靠近信号过孔放置时,则在时延方面的影响是必须要考虑的。先举个例子,在TOP层的微带线长度是 150 mils,BOTTOM层的微带线也是150 mils,线宽都为4 mils,且过孔的参数为:barrel diameter=8mils,pad diameter=18mils,anti-pad diameter=26mils。

这里有三种方案进行对比考虑,一种是,通过过孔互联的这个过孔附近没有任何地过孔,那么,其返回路径只能通过离此过孔250 mils的PCB边缘来提供;第二种是,一根长达362 mils的微带线;第三种是,在一个信号线的四周有四个地过孔环绕着。图6显示了带有60 Ohm的常规线的S-Parameters,从图中可以看出,带有四个地过孔环绕的信号过孔的S-Parameters就像一根连续的微带线,从而提高了 S21特性。由此可知,在信号过孔附近缺少返回路径的情况下,则此信号过孔会大大增高其阻抗。当今的高速系统里,在时延方面显得尤为重要。

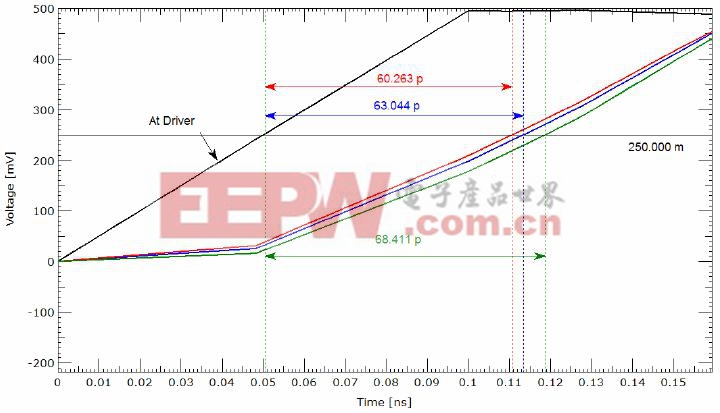

现做一个测试电路,类似于图5,驱动源是一个线性的60 Ohms阻抗输出的梯形信号,信号的上升沿和下降沿均为100 ps,幅值为1V。此信号源按照图6的三种方式,且其端接一60 Ohms的负载,其激励为一800 MHz的周期信号。在0.5V这一点,我们观察从信号源到接收端之间的时间延迟,显示出来它们之间的时延差异。其结果如图7所示,在图中只显示了信号的上升沿,从这图中可以很明显的看出,带有四个地过孔环绕的过孔时延同直线相比只有3 ps,而在没有地过孔环绕的情况下,其时延是8 ps。由此可知,在信号过孔的周围增加地过孔的密度是有帮助的。然而,在4层板的PCB里,这个就显得不是完全的可行性,由于其信号线是靠近电源平面的,这就使得信号的返回路径是由它们之间的耦合程度来决定的。所以,在4层的PCB设计时,为符合电源完整性(power integrity)要求,对其耦合程度的控制是相当重要的。

图6: 带有过孔互联通道的s-parameters

图7: 图6三种案例的发送和接收波形

对于DDR2和DDR3,时钟信号是以差分的形式传输的,而在DDR2里,DQS信号是以单端或差分方式通讯取决于其工作的速率,当以高度速率工作时则采用差分的方式。显然,在同样的长度下,差分线的切换时延是小于单端线的。根据时序仿真的结果,时钟信号和DQS也许需要比相应的ADDR/CMD /CNTRL和DATA线长一点。另外,必须确保时钟线和DQS布在其相关的ADDR/CMD/CNTRL和DQ线的当中。由于DQ和DM在很高的速度下传输,所以,需要在每一个字节里,它们要有严格的长度匹配,而且不能有过孔。差分信号对阻抗不连续的敏感度比较低,所以换层走线是没多大问题的,在布线时优先考虑布时钟线和DQS。

5. 串扰

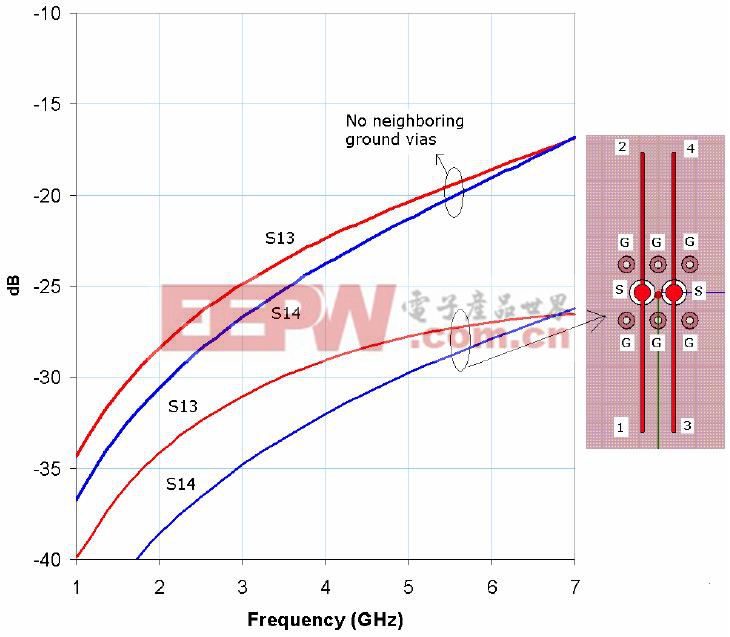

在设计微带线时,串扰是产生时延的一个相当重要的因素。通常,可以通过加大并行微带线之间的间距来降低串扰的相互影响,然而,在合理利用走线空间上这是一个很大的弊端,所以,应该控制在一个合理的范围里面。典型的一个规则是,并行走线的间距大于走线到地平面的距离的两倍。另外,地过孔也起到一个相当重要的作用,图8显示了有地过孔和没地过孔的耦合程度,在有多个地过孔的情况下,其耦合程度降低了7 dB。考虑到互联通路的成本预算,对于两边进行适当的仿真是必须的,当在所有的网线上加一个周期性的激励,将会由串扰产生的信号抖动,通过仿真,可以在时域观察信号的抖动,从而通过合理的设计,综合考虑空间和信号完整性,选择最优的走线间距。

图8: 相互耦合走线的s-parameters

6. 电源完整性

这里的电源完整性指的是在最大的信号切换情况下,其电源的容差性。当未符合此容差要求时,将会导致很多的问题

- 先进高速传输接口及高速DDR存储器技术(02-10)

- 电源设计小贴士 41:DDR内存电源(11-21)

- TI推出业内首个完全集成的DDR存储器电源解决方案(09-12)

- 8位1.0GSPS ADC芯片MXT2001原理与应用(11-07)

- 用Xilinx FPGA实现DDR SDRAM控制器(11-30)

- 基于IDDR的亚稳态问题解决方案介绍(08-18)