8位1.0GSPS ADC芯片MXT2001原理与应用

引言

高速模数转换器(ADC)被广泛运用在高速测试设备,高速雷达,卫星接收机,高速成像系统,高速存储设备等领域,作为模拟信号与数字信号的接口发挥着重要的作用。目前,随着我国信息化技术的不断深入,主流的电子产品加速由MHz频段向GHz频段推进,迫切需要采样率为1GSPS以上的高速采样ADC,以满足不断提高的系统速度和实时采样要求。但是,高速ADC是典型的高端混合信号电路,其研发和生产的难度较大,成为制约高速电子系统的瓶颈技术。基于这样的背景,北京时代民芯科技有限公司研发了双通道8位1GSPS通用型超高速ADC芯片,型号为MXT2001,为国内首款8位1GSPS ADC产品,推动了国内高速数据采集产业的深入发展。

芯片介绍

MXT2001是一款双通道,低功耗,高性能的CMOS模数转换器,其采样精度为8位,单通道采样率高达1.25GSPS,采用单电源1.8V供电,典型功耗为1.58W。它采用高速模-数转换电路以及数字自校准技术,保证器件的高速度和高动态特性。器件内部集成串行SPI接口,支持用户控制、改变电路参数,以优化电路性能和满足系统要求。

MXT2001具有双通道结构,每个通道的最大输入带宽(FPBW)高达1.6GHz;采用双通道“双沿采样(DES)”模式时,典型采样率为2.0GSPS,采样速率最高可达2.5GSPS;采用LQFP144封装,1.8V单电源供电;具有自校准功能,实施上电自动校准并支持用户随时启用一键(CAL引脚)校准;可通过普通方式或扩展方式对其进行控制,可工作在SDR,DDR等多种模式下。在扩展方式下,用户可对芯片电路参数进行修改,改变输入范围,采样保持电路参数和进行精度优化等,以满足系统应用的要求。

MXT2001芯片性能卓越,典型情况下可提供7.0位以上的有效位数(ENOB)。为了方便用户捕捉输出数据,该芯片采用低压差分电路(LVDS)进行数据传输,两通道输出的二进制编码数据分别经由1:2信号分离器(DEMUX)后,输出为4路8位并行500Msps LVDS数据流,输出数据率降低至只有采样率的一半,方便后级电路的数据接收。在普通模式下,I/Q通道分别获得1.0GSPS数据输出速度,在双沿采样(DES)模式下,I/Q通道交错工作,可获得典型2.0GSPS/高达2.5GSPS的采样速率。

MXT2001的基本原理

芯片基本原理

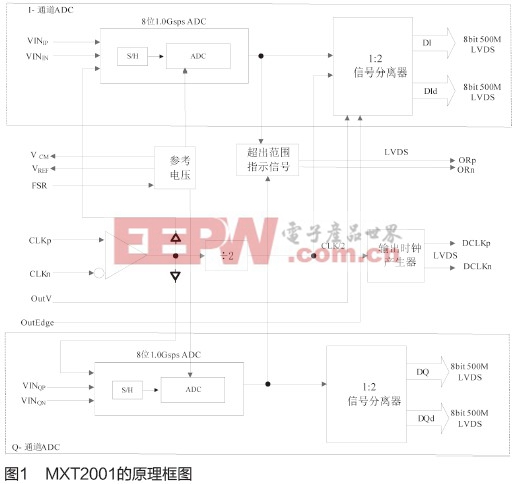

MXT2001芯片的原理框图如1所示,为全CMOS结构的双通道8位1.0GSPS模数转换器,由两路独立的转换通道(I/Q)组成,每通道均集成高性能宽带采样保持电路和模数信号预处理电路,信号电路的最大输入带宽(FPBW)为1.6GHz。I/Q通道的信号输出为二进制编码,分别经1:2信号分离器后,输出4路8位500Msps的LVDS信号,方便接收存储器的信号捕捉。I/Q通道共用时钟及参考源,其中输入时钟为1GHz频率,经片上时钟模块移相后分别控制I/Q通道的时序。输出LVDS信号共34对,除32对数据输出外,还包括1对输出同步时钟(DCLK)和1对输入范围溢出指示信号(OR)。

MXT2001芯片集成了数字校准电路,自动对电路参数进行预设,保证动态精度有效性。芯片提供用户编程接口,支持高级用户对芯片配置的在线修改。

芯片封装结构

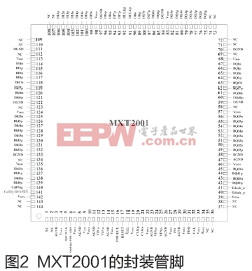

MXT2001芯片采用144脚LQFP封装,如图2所示。其管脚说明如下:

(1)OUTV/SCLK:输出电压幅度和串行接口时钟。为高电平时,表示正常差分输出数据幅度,为低电平时,表示降低差分输出幅度和降低功耗。当扩展控制模式被激活,SCLK作为串行数据的输入时钟。

(2)OUTEDGE/DDR/SDIN:DCLK边沿选择,双数据速率(DDR)和串行数据串行输入。当输出数据转换时,此引脚设定DCLKp的输出边缘。当引脚浮空或连接到1/2电源电压时,使能DDR时钟。在扩展控制模式下,此引脚作为串行数据输入端(SDIN)。

(3)RESET:复位。当引脚输入正脉冲用于复位和同步多个转换器的时序DCLK。

(4)PD/PDQ:低功耗掉电模式。PD引脚为高电平时,芯片进入低功耗掉电模式。当PDQ引脚接高电平时,只有Q通道进入低功耗掉电模式。

(5)CAL:校准模式启动信号。最低80个时钟周期的逻辑低电平输入之后紧随80个时钟周期的逻辑高电平输入,将激发电路进入自动校准模式。

(6)FSR/ECE:全量程选择以及扩展控制模式选择,在非扩展控制模式,逻辑低电平会把全量程差分输入范围(峰峰值)设置为650mV;逻辑高电平会把全量程差分输入范围(峰峰值)设置为870mV。当此脚连接到1/2电源电压或者悬空时,进入扩展控制模式。

(7)CLKp/CLKn:ADC的LVDS时钟输入。这个差分时钟信号必须是交流耦合的。输入信号将在CLKp的下降沿被采样。

(8)VINIp/VINIn/VINQp/VINQn:ADC的模拟输入脚。

(9)CalFlag:校准运行指示。高电平有效。

(10)DI/DQ/DId/DQd:I通道和Q通道的L

ADC GSPS MXT2001 模拟信号 DDR 201311 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)