针对DDR2-800和DDR3的PCB信号完整性设计

,比如加大时钟抖动、数据抖动和串扰。

这里,可以很好的理解与去偶相关的理论,现在从”目标阻抗”的公式定义开始讨论。

Ztarget=Voltage tolerance/Transient Current (1)

在这里,关键是要去理解在最差的切换情况下瞬间电流(Transient Current)的影响,另一个重要因素是切换的频率。在所有的频率范围里,去耦网络必须确保它的阻抗等于或小于目标阻抗(Ztarget)。在一块 PCB上,由电源和地层所构成的电容,以及所有的去耦电容,必须能够确保在100KHz左右到100-200MH左右之间的去耦作用。频率在 100KHz以下,在电压调节模块里的大电容可以很好的进行去耦。而频率在200MHz以上的,则应该由片上电容或专用的封装好的电容进行去耦。实际的电源完整性是相当复杂的,其中要考虑到IC的封装、仿真信号的切换频率和PCB耗电网络。对于PCB设计来说,目标阻抗的去耦设计是相对来说比较简单的,也是比较实际的解决方案。

在 DDR的设计上有三类电源,它们是VDD、VTT和Vref。VDD的容差要求是5%,而其瞬间电流从Idd2到Idd7大小不同,详细在JEDEC里有叙述。通过电源层的平面电容和专用的一定数量的去耦电容,可以做到电源完整性,其中去耦电容从10nF到10uF大小不同,共有10个左右。另外,表贴电容最合适,它具有更小的焊接阻抗。

Vref要求更加严格的容差性,但是它承载着比较小的电流。显然,它只需要很窄的走线,且通过一两个去耦电容就可以达到目标阻抗的要求。由于Vref相当重要,所以去耦电容的摆放尽量靠近器件的管脚。

然而,对VTT的布线是具有相当大的挑战性,因为它不只要有严格的容差性,而且还有很大的瞬间电流,不过此电流的大小可以很容易的就计算出来。最终,可以通过增加去耦电容来实现它的目标阻抗匹配。

在4层板的PCB里,层之间的间距比较大,从而失去其电源层间的电容优势,所以,去耦电容的数量将大大增加,尤其是小于10 nF的高频电容。详细的计算和仿真可以通过EDA工具来实现。

7. 时序分析

对于时序的计算和分析在一些相关文献里有详细的介绍,下面列出需要设置和分析的8个方面:

1. 写建立分析: DQ vs. DQS

2. 写保持分析: DQ vs. DQS

3. 读建立分析: DQ vs. DQS

4. 读保持分析: DQ vs. DQS

5. 写建立分析: DQS vs. CLK

6. 写保持分析: DQS vs. CLK

7. 写建立分析: ADDR/CMD/CNTRL vs. CLK

8. 写保持分析: ADDR/CMD/CNTRL vs. CLK

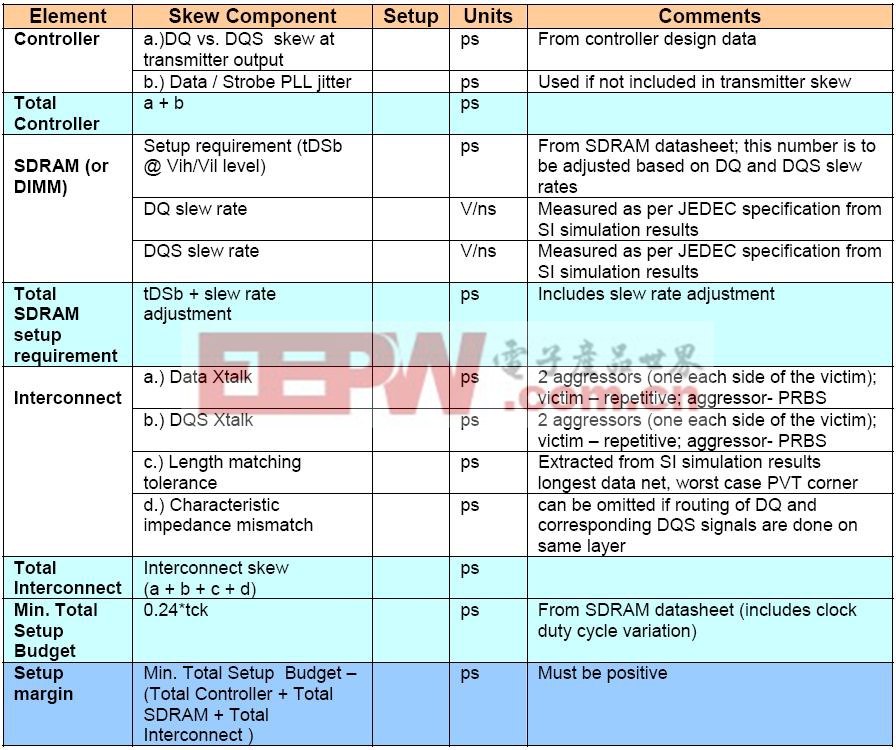

表2举了一个针对写建立(Write Setup)分析的例子。表中的一些数据需要从控制器和存储器厂家获取,段”Interconnect”的数据是取之于SI仿真工具。对于DDR2上面所有的8 项都是需要分析的,而对于DDR3,5项和6项不需要考虑。在PCB设计时,长度方面的容差必须要保证total margin是正的。

表2: 针对DQ vs. DQS的DDR3写保持时域分析案例

8. PCB Layout

在实际的PCB设计时,考虑到SI的要求,往往有很多的折中方案。通常,需要优先考虑对于那些对信号的完整性要求比较高的。画PCB时,当考虑一下的一些相关因素,那么对于设计PCB来说可靠性就会更高。

1. 首先,要在相关的EDA工具里要设置好里设置好拓扑结构和相关约束。

2. 将BGA引脚突围,将ADDR/CMD/CNTRL引脚布置在DQ/DQS/DM字节组的中间,由于所有这些分组操作,为了尽可能少的信号交叉,一些独立的管脚也许会被交换到其它区域布线。

3. 由串扰仿真的结果可知,尽量减少短线(stubs)长度。通常,短线(stubs)是可以被削减的,但不是所有的管脚都做得到的。在BGA焊盘和存储器焊盘之间也许只需要两段的走线就可以实现了,但是此走线必须要很细,那么就提高了PCB的制作成本,而且,不是所有的走线都只需要两段的,除非使用微小的过孔和盘中孔的技术。最终,考虑到信号完整性的容差和成本,可能选择折中的方案。

4. 将Vref的去耦电容靠近Vref管脚摆放;Vtt的去耦电容摆放在最远的一个SDRAM外端;VDD的去耦电容需要靠近器件摆放。小电容值的去耦电容需要更靠近器件摆放。正确的去耦设计中,并不是所有的去耦电容都是靠近器件摆放的。所有的去耦电容的管脚都需要扇出后走线,这样可以减少阻抗,通常,两端段的扇出走线会垂直于电容布线。

5. 当切换平面层时,尽量做到长度匹配和加入一些地过孔,这些事先应该在EDA工具里进行很好的仿真。通常,在时域分析来看,差分线里的两根线的要做到延时匹配,保证其误差在+/- 2ps,而其它的信号要做到+/- 10 ps。

9. DIMM

之前介绍的大部分规则都适合于在PCB上含有一个或更多的DIMM,唯一列外的是在DIMM里所要考虑到去耦因素同在DIMM组里有所区别。在DI

- 先进高速传输接口及高速DDR存储器技术(02-10)

- 电源设计小贴士 41:DDR内存电源(11-21)

- TI推出业内首个完全集成的DDR存储器电源解决方案(09-12)

- 8位1.0GSPS ADC芯片MXT2001原理与应用(11-07)

- 用Xilinx FPGA实现DDR SDRAM控制器(11-30)

- 基于IDDR的亚稳态问题解决方案介绍(08-18)