双DSP柔性处理系统研究

1 引言

为了进一步提高现有机载光电跟踪系统在实战环境中,针对复杂场景下快速运动目标实施实时跟踪的鲁棒性与稳定性,笔者提出以双DSP和FPGA为核心来构建主从式超高速并行处理体系的设计思想,并研究开发了基于双DSP的新型柔性机载实时图像跟踪系统。一方面,采用双DSP体系结构实现系统任务的并行划分使本系统具备极高的运算处理速度;另一方面,现场可编程逻辑器件FPGA的引入使系统的灵活性也得到极大的提高。而将两者结合可使本系统充分体现新一代机载实时图像跟踪系统更快速、更精确、更灵活的特点。

2 双DSP高速信号处理系统特点

美国德州仪器公司(TI)推出的新一代数字信号处理器TMS320C6414(以下简称C6414)的主频为400MHz~700MHz,其数据处理能力为3200MIPS~5760MIPS。该器件的结构框图如图1所示。其主要特点如下:

(1)DSP内核采用超长指令字(VLIW)体系结构,有8个功能单元、64个32bit通用寄存器,一个时钟周期可同时执行8条指令,运算能力可以达到5760MIPS;

(2)为了使数据能满足超高速DSP内核的需求,C6414采用了两级超高速缓冲存储器,即16k Byte的一级数据Cache、16k Byte的一级程序Cache和1024k Byte的数据和程序统一内存。

(3)增加了直接处理打包数据指令,可建立无缝的数据流,以提高指令集的效率;

(4)每个功能单元在硬件上都增加了附加功能,从而增强了指令集的正交性。

3 系统硬件设计

本光电成像跟踪系统硬件平台由六部分组成:图像采集与预处理模块、同步分离模块、FPGA逻辑控制模块、双DSP+双口RAM 图像处理模块、异步通信模块和图形显示模块。其系统原理框图如2所示。从图2可以知道:红外探测器及可见光摄像仪输出的模拟视频信号经多路信号选择芯片导入之后,经箝位、放大、滤波以及去同步头等预处理后,一路经A/D转换器将模拟视频转换为8bit数字信号并导入片外视频缓存1、2,而后等待FPGA时序控制DSP外部中断,以便将全部缓存数据搬移到DSP片内的2级缓存,再通过系统任务划分实现数据重组,然后分别在主从DSP进行同步并行数据处理,并将中间结果由主DSP综合,最后在完成后续运算后给出最终匹配结果。与此同时,主DSP则通过写图形显示缓存将目标匹配位置信息传递到外界;另一路模拟信号先导入同步分离器,然后提取行场同步信号送交FPGA作为时基,以产生系统各级时序控制信号;第三路模拟信号送给图形叠加电路作为输入叠加信号之一,当场正程来到时,FPGA中断控制并读出图形存储器数据,同时在FPGA片内实现读入数据的并/串转换后移位输出至图形叠加电路,此时两路信号将会合送入视频监视器,从而完成视频图像上图形的显示。整个系统工作期间,每隔80ms主DSP还通过异步收发器与外部上位机进行串行通信,以便系统能够实时接收外部命令与目标参数,进而调整跟踪系统的工作状态。

3.1 图像采集与预处理模块

本系统中的多路选择器件选用CD4052芯片。它能根据不同的工作场合来切换红外/可见光视频输入;视频预处理电路采用AD817进行视频信号的放大,以得到更清晰的信号来进行视频处理;A/D芯片选用AD公司的AD9225,输出的8bit数字视频信号送入74LS245进行数据锁存。

3.2 同步分离模块

系统采用一款专门的视频同步分离器LM1881来从标准的负同步NTSC(PAL或SECAM)视频信号中分离出有效的行/场同步信号,并将其送入FPGA以产生系统的各级逻辑控制输出。

3.3 FPGA逻辑控制模块

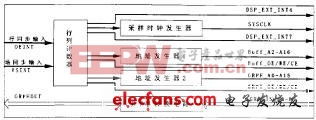

由于系统中各个芯片的功能相对独立,要协调这些芯片的运作就需要一片起控制逻辑作用的可编程芯片,为此,笔者选用了ALTERAL公司的EPF10K30A,该芯片有246个用户I/O口、30000个典型门、216个逻辑阵列块、1728个逻辑单元不仅能满足系统的控制要求,而且也可以为将来系统的功能扩展提供控制逻辑。在这个光电跟踪系统中,FPGA主要用来完成如下几方面的工作:

(1)生成A/D采样控制时钟,实现模拟视频的正确采样;

(2)提供字符图形存储器地址及片选/读控制信号,并在场正程到来时,控制图形数据的读出;

(3)提供视频数据缓存器地址及片选/写控制信号,控制视频数据的连续写入;

(4)产生外部中断4至双DSP,当数据写满视频图像高速缓存预定空间时,控制主从DSP以将数据块快速搬移至片内2级缓存;

(5)产生外部中断7至主DSP,并在每个场逆程时刻来到时,控制主DSP擦、写字符图形存储器数据;

(6)产生一并/串转换电路,以将并行读入的字符图形数据串行移位输出至图形叠加电路,从而实现“+”、“□”图形在视频图像上的叠加。

其FPGA内部结构框图如图3所示。

图3 FPGA内部结构框图

3.4 双DSP+双口RAM 图像处理模块

高速并行数字信

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)