双DSP柔性处理系统研究

号处理电路以双DSP为并行运算处理核心单元,并辅以双口RAM来实现视频图像的高速缓存,从而完成大运算量的高速实时目标跟踪处理任务。该并行处理系统的组成与功能分述如下:

a. 视频图像高速缓存子模块

为了实现图像的实时采集与高速处理,本系统用两片双口RAM组成相互独立的视频缓存,分别对应主/从DSP处理器。设计时选用IDT公司的3.3V 异步双口PRAM IDT70V657,同时与DSP接口采用ASRAM方式。由于EMIF的ASRAM接口支持32Bit的数据接口,因此,利用IDT70V657构成不完全地址结构来存取数据能够更好地实现8Bit锁存数据与C6414的接口,而无须对DPRAM进行宽度扩展。同时亦可减少DSP读取外部数据的时间开销。

IDT70V657的大小是32K×36Bit系统采用将两个DPRAM各划分为前后两个半场的方式来实现存取数据时的乒乓切换。即在系统工作的任一时刻,当对DPRAM前半场写入数据时,使DPRAM后半场向DSP读出数据。当前半场写满视频数据时,由FPGA给DSP发出中断信号,以通知DSP读出DPRAM前半场所写入数据,同时,将A/D转换器的数据写入DPRAM后半场缓冲空间,如此反复进行来实现数据的读出与写入同步操作。

b. 双DSP高速信号处理系统

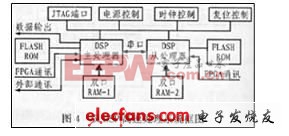

TMS320C6414-600型DSP的主频高达600MHz,在超高速实时图像处理领域有着非常出色的性能。本系统的双DSP高速实时信号处理系统就以2片C6414-600 DSP芯片为核心组成邻域图像并行处理机,并通过系统任务的划分与分解实现同步并行运算处理。其系统框图如图4所示。

在本系统中,主DSP完成的主要功能如下:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2) 实现与外部上位机的即时通讯,接收外部命令与目标参数;

(3) 实现与从DSP的即时通信,下传命令字与目标参数以及获取中间结果;

(4) 运行系统跟踪算法,承担系统核心运算任务的一半;

(5) 与FPGA建立即时通信,实现系统程序模块的调度与协调;

从DSP完成的主要功能是:

(1) 实现外部缓存数据到片内的搬移,为DSP高速批处理开辟片内二级缓存;

(2)运行系统跟踪算法,承担系统核心运算任务的一半;

(3)实现与主DSP的即时通信,上传匹配运算中间结果;

(4)与FPGA建立即时通信,实现系统程序模块的调度与协调。

双DSP处理系统的柔性特色体现在:可依据实时环境需要加载不同的跟踪算法来实现目标跟踪。算法运行之初,两片C6414-600都在FPGA的控制下,通过EMIFA口以EDMA方式,分若干次,依系统跟踪算法而定将外部视频缓存中的数据(一场图像)依次读入DSP的L2片内缓存中;算法运行之后,主从DSP则通过McBSP直接互接来实现双DSP间的高速同步通以便交换数据处理结果。

系统设计中,Flash ROM选用AMD公司的AM29LV800(1M×8Bit)来把FLASH映射到DSP统一编址地址空间EMIFB口的CE1空间。当系统上电复位后,该地址空间为首先引导区域,这样即可将应用程序代码加载到片内高速执行,从而实现系统的脱机运行。

3.5 异步通信模块

本系统与外部上位机的异步通信主要通过主DSP的McBSP。C6000的McBSP是一个功能非常强大的标准串口,支持全双工串行通信,它的双缓冲数据寄存器允许连续的数据流,可与多达128个通道进行收发通信。通过对McBSP的SPCR、RCR、XCR、SRGR、PCR寄存器的配置可实现系统通信时收发数据的帧同步和时钟同步。

由于外部上位机的通讯机制是RS422标准,而DSP与外部通信只提供RS232接口,故应采用一片MAX3074芯片来实现RS422到RS232的转换。MAX3074是MAXIM公司生产的一款专门用于RS422/485至RS232的转接芯片,采用3.3V供电,这与C6000 DSP 外围供电电压一致,连接非常方便,不再需要多余的电压适配器。另一方面,由于McBSP为同步串口,为了实现McBSP与RS232的无缝连接,可通过软件加入发送扩展算法与接收压缩算法,从而实现DSP与上位机异步串口通信协议的握手。

3.6 图形显示模块

该模块由图形存储器、图形叠加电路和视频监视器组成。图形存储器选择IDT公司的70V08(64K×8Bits)DPRAM来存储标识目标匹配位置的图形数据。图形叠加电路用于实现视频与图形的叠加,并最终由视频监视器显示叠加结果。

4 系统工作流程

本系统的软件工作模式包括复位和初始化模式、运行模式、系统维护模式,可由系统程序来控制三种模式的切换。

在复位和初始化模式下,系统启动后将由主从DSP同步实现程序搬移,把程序代码搬移到片内并运行系统程序,从而初始化主从DSP的运行环境并设置相关参数。

运行模式下,双DSP一方面独立响应并处理FPGA中断、运行核心跟踪算法并实现子系统内的进程调度;另一方面通过主从DSP串口间的互连响应中断以及主DSP串口与远程主机

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)