IC时钟分配系统中的PLL

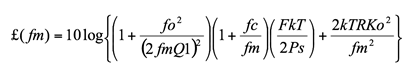

抖动会产生扩频,进而生成相位噪声。可通过利森(Leeson)方程式充分理解VCO噪声,同时还可通过对该方程式的研究,找到降低VCO噪声的方法。表示振荡器相位噪声频谱的利森方程式如下:

式中:

£(fm) 为偏移时的功率比

fm为振荡器所生成的总输出功率中的1Hz频带(单位:dBc/Hz)

fo为载波频率

fm为偏移频率

fc闪烁转角频率

Q1为谐振器的负载Q值(负载Q值指包括外部组件影响在内的品质因数)

F为噪声因数

kT为室温条件下的波尔兹曼常数

Ps为振荡器输入端的平均功率

R为调谐二极管的等效噪声电阻

Ko为振荡器的电压增益。

通过观察利森方程式,我们便可发现VCO中相位噪声的优化点:

1. 调谐电路的负载Q值应最大化。可考虑串联谐振电路内的大电感器或并联谐振电路内的大电容器设计以实现该目标。负载Q值每上升10dB可改善20dB的相位噪声。

2. 必须选用低等效噪声电阻的变容二极管。同时推荐使用非线性程度低的变容二极管。

3. VCO调谐增益须保持在所需的最小值水平。

4. 必须选用可在低频和低闪烁转角频率时产生低噪声的有源设备。

5. 振荡器的高输入功率有益于降低噪声。

当PLL用作时钟合成器时,可削弱输入源的噪声并生成低噪声输出。若PLL的输入源噪声量很大,通常推荐使用低带宽PLL对其进行滤波,但是降低PLL带宽会导致VCO噪声的相对贡献上升。因此,通常应在PLL合成器内使用高品质的基准源,该基准源的噪声性能应优于振荡器的噪声性能,方能对PLL的带宽进行优化。

相位检测器和充电泵噪声:

相位检测器和充电泵是PLL内与载波频率接近的相位噪声源。对比而言,VCO的主要噪声贡献则在载波器的远端区间内,主要为超过环路滤波器截止频率的部分。由于闭合环路中的PLL具有低通滤波器的功能,故相位检测器、充电泵或基准噪声源内超过环路滤波器截止频率的噪声通常均会被过滤。由于相位检测器和充电泵的集成功能是检测出基准信号和VCO输出端反馈信号间的差异,并随后生成误差信号,故输入信号相位的随机变化会导致相位检测器生成错误的输出结果,该结果经滤波器传输后,会对VCO进行错误调谐,使人误认为噪声产生于PLL的输出端。确保噪声与基准值间尽可能产生最小偏离并同时最大化充电泵的增益,这样可以降低相位噪声。

分频器噪声:

PLL中的分频器噪声直接出现于相位检测器的输入端,且与输入终端噪声具有相同的传递函数;因此,该噪声在环路滤波器截止频率以下的近载波区间内同样会对总体相位噪声有贡献。数字分频器的多余噪声可调节为其输出端的加性噪声源。

电源噪声:

必须确保电源噪声最小化,以降低PLL内的相位噪声。电源噪声的产生根源十分多样,如调节器设计不合理、PCB噪声耦合、电源内的噪声未经适当滤波等。该噪声可加大PLL模块内的总体噪声。

结论:

我们在本部分不仅了解了相位噪声是PLL的关键参数之一,还分析了如何通过PLL级和系统级的悉心设计,采用优良的滤波电路、低噪声源,以及最小化系统内所有其它可能的噪声源等方法,从而最大限度地降低相位噪声。

- IC时钟分配系统中的锁相环(04-29)

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环中YTO自校准技术的应用(10-02)

- 基于DDS+PLL技术的频率合成器的设计(07-23)