多通道实时阵列信号处理系统的设计

标,对各个通道的一致性也需进行测试。

本系统测试中采用FFT法对采集系统的有效位数和幅相一致性进行测试,信号源输出51 MHz,幅度以经过功分器后幅度达到-1 dBFS左右为准,测试信号由安捷伦8648B信号源产生;功分器输出信号通过带通滤波器(通带范围47.5~52.5 MHz)以减少信号源噪声对测试结果的影响。ADC采样的数据在FPGA内完成传兵转换后,可在ChipScope中观察并导出。对导出的数据做FFT,在(0,N/2)区间内寻找功率谱的峰值点,即为信号功率Psignal。由于前端使用了带通滤波器,故在计算有效位数时噪声功率是可认为在滤波器阻带范围内的噪底是ADC及其前端电路产生的噪声,故计算噪声时由一段阻带范围内的噪声得到噪声功率的平均值,将噪声功率的平均值乘以N/2得到噪声功率 Pnoise,并根据

计算出AD的有效位数。

FFT计算时还需注意截断误差的影响,截断会使谱分析精度受到影响。如果时域信号是周期性的,而截断又按整周期取数,信号截断不会产生问题,因为每周期信号都能代表整个周期信号变化情况。这就是所谓的相干采样。采取相干采样的办法,需要正确地选择测试信号频率,使时域样本正好包含整数个周期的信号,可以完全消除频谱泄露的影响。下式是相干采样要满足的条件:

公式中Mc为记录期间正弦周期的整倍数,M为在采样的样本数,M和Mc互为素数。fin为输入正弦测试信号的频率,fs为采样频率。使用相干采样是最理想的处理办法,可以避免频谱泄露。

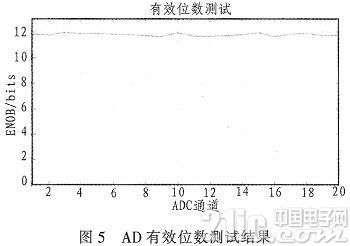

有效位数测试结果如图5所示。

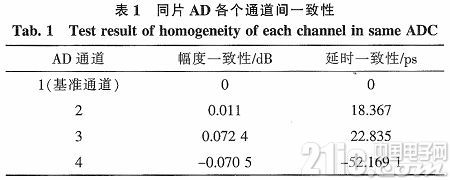

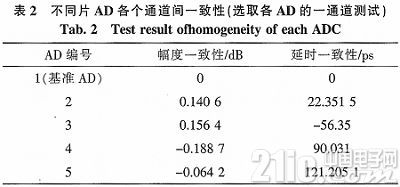

对ADC的多通道一致性主要关注其幅度一致性和其延迟(相位)一致性,道ADC的幅度一致性是指在相同的正弦波输入下,由于ADC前端电路的差异、不同片 ADC和同片ADC不同通道之间差异造成的ADC采集结果幅值的差异。测试中分别求取信号的功率谱密度,在各自的功率谱中找到最大值点。设从两个通道中得到的最大值点分别为和,则幅度一致性为:△G=20logA2/A1。

而其延迟(相位)一致性是指ADC采集结果相位的差异,影响信号相位的因素有两个,分别是通道延迟和附加相位,设通道延迟为,附加相位为θ。由于对正弦信号而言,无法区分相位变化是哪种因素引入的,在正弦信号作为测试信号时,考虑到不同ADC的工作差异也主要体现在真实采样时刻和采样时钟的延迟差不同,因此利用正弦信号作为测试信号时,忽略附加相位θ,即认为只有通道延迟τ。测试中利用时域延迟和频域相位的对应关系,即:x(t- τ)←→X(j2πf)exp(-2πfτ)从频谱中读取正频谱部分最大值点的相位φ+,则延迟量为:

3 结论

本文介绍的系统具有良好的性能,实现了阵列信号处理算法的实时处理。测试结果表明,采集系统不仅具有高达11.5bit的有效位数,而且还具有低至200p的通道延时差,性能指标完全符合设计要求,为信号的实时处理奠定了基础,已在某雷达接收机当中得到了成功应用。

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)