多通道实时阵列信号处理系统的设计

摘要:以全数字化信号产生和数字波束形成处理为基础的数字化阵列雷达已成为当代相控阵雷达技术发展的一个重要趋势,本文针对现代数字化阵列雷达对多通道数据采集和实时处理的需求,设计了一种基于FPGA的多通道实时阵列信号处理系统。可完成对20通道的中频数据采集,实时波束合成和数据传输功能,实验结果表明系统工作稳定、性能良好,具有良好的信噪比和通道一致性。

随着数字信号处理技术的不断进步和相应处理能力的不断提高,数字化阵列雷达以其动态范围大、扫描波束多、设计灵活性高的特点,已经逐步取代传统模拟阵列雷达成为高性能阵列雷达的主要研究方向。数字化阵列雷达需要将各个阵列天线接收的信号经过模拟下变频后经过AD采样并在数字域内进行信号处理,其典型的信号处理的方法包括数字波束形成(DBF)技术和波达方向估计(DOA)技术等。对于数字阵列雷达而言,对模拟下变频后的信号完成多通道数据采集、数据处理和传输是系统的关键部分,对处理系统的同步性能、通道间幅相一致性均提出了很高要求,如进行DBF处理中通道间的不一致性将会影响波束合成后天线的方向图的特性,使增益下降、旁瓣电平升高。同时数字阵列雷达需要对各个通道采集下的数据实时地完成信号处理和数据传输功能,对处理系统的实时处理能力和信号吞吐能力提出了一定挑战。

本文介绍了一种针对DBF处理的多通道阵列信号处理系统的设计方案,以Xilinx的XC7K325T FPGA为核心,完成了20通道的中频数据采集,并在FPGA内完成数字波束合成功能,可以同时完成8个波束指向的合成,并且将合成后的数据通过 RapidIO结果传输至实时处理机进行进一步的处理。

1 系统设计原理和组成

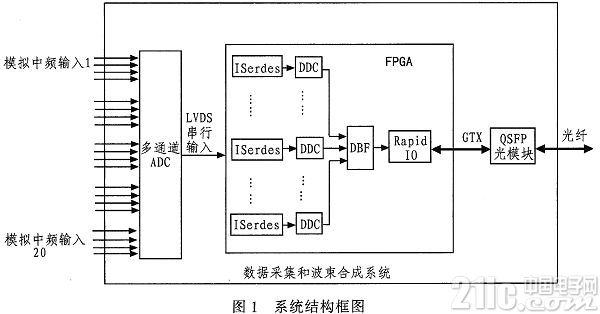

本系统由数据采集模块和波束合成与传输模块两部分组成,系统框图如图1所示。

20路模拟中频输入通过SSMC连接器输入,由5片四通道A/D芯片AD9653采样后,通过LVDS接口串行输出到到FPGA的ISERDES输入模块中完成串并转换,并在FPGA内完成数字下变频、I/Q变换、低通滤波以及数字波束合成功能。波束合成后的数据在FPGA中封装成RapidI/O协议的数据帧,通过QSFP接口传输至相应的信号处理系统或存储记录系统中。数字波束合成及数字切副瓣处理中需要的权值由上位机通过RS-422接口输入到 FPGA。同时软件部分还可提供幅度和相位补偿参数接口。FPGA外接1个256MBx16bit的DDR3 SDRAM,以缓存一定量的原始数据和波束合成处理后的数据。

1.1 数据采集模块设计

数据采集模块是系统设计的关键部分和主要困难所在,该模块需要完成20通道的数据采集,并在保证信噪比的同时使AD各通道间串扰和通道间的不一致性尽可能低。这需要在AD的选型、AD前端耦合电路设计,AD电源的去耦和滤波,PCB布局布线等方面做精心的设计。考虑到本模块中数据采集部分中通道数量多,与使用许多个单通道ADC相比,使用单片内多通道ADC具有提高系统集成度、降低系统实施难度、减少系统功耗等诸多优势,在经过初期调研和选型后,决定采用 ADI公司的4通道、16bit、高速ADC—AD9653。

AD9653主要性能指标如下:

采样通道数:4

最大采样率:125 Msps

模拟带宽:650 MHz

位数:16 bit

信噪比:76.5 dBFS

无杂散动态范围:90 dbc

针对本模块中要求的20路中频数据采集,使用5片AD9653即可满足需求,极大地简化了系统设计。其优越的信噪比和动态范围可满足绝大部分中频接收机对采样精度的要求。

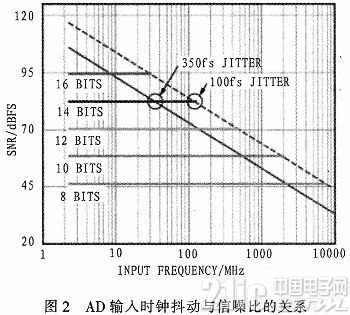

在选定AD芯片的同时,需要根据AD所要求达到的信噪比选定相应的时钟分发芯片,这是由于AD的信噪比不只由AD本身及其外围电路决定,也和AD输入时钟的抖动有关。图2显示了理想ADC输入时钟抖动与信噪比的关系,通过ADC位数和输入时钟抖动两条线的交点处确定给定模拟输入信号频率时ADC最多可容忍的总时钟抖动量,即考虑抖动因素的具有无限的分辨率的理想ADC的信噪比 ,SNRided 应大于等于指定位数的理想ADC的量化噪声SNRbit=6.02N+1.76,对于16位ADC,其量化噪声为98dBFS,可以得到在输入时钟抖动小于50fs的情况下,ADC的信噪比不会发生恶化。但目前受时钟分发芯片性能的限制,目前时钟扇出超过5路的时钟分发芯片可达到的最小抖动都超过 50fs,故本设计中采用用于要求低抖动的高速应用的时钟分发芯片ADCLK948,时钟抖动为75fs,最大输出频率4.8 GHz,以最大程度的保证ADC的有效位数尽可能少的收到时钟抖动的影响。

,SNRided 应大于等于指定位数的理想ADC的量化噪声SNRbit=6.02N+1.76,对于16位ADC,其量化噪声为98dBFS,可以得到在输入时钟抖动小于50fs的情况下,ADC的信噪比不会发生恶化。但目前受时钟分发芯片性能的限制,目前时钟扇出超过5路的时钟分发芯片可达到的最小抖动都超过 50fs,故本设计中采用用于要求低抖动的高速应用的时钟分发芯片ADCLK948,时钟抖动为75fs,最大输出频率4.8 GHz,以最大程度的保证ADC的有效位数尽可能少的收到时钟抖动的影响。

由于AD9653采用差分输入,而中频接收机输出为单端信号,故采用高频变压器耦合方式完成单端信号到差分信号的转换,变压器耦合前端能够驱动较高频率而无明显的插入损耗,多匝比率变压器还能

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)