基于WCDMA接收机系统的低噪声放大器设计

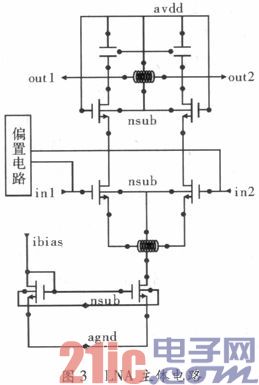

用电阻,目的是减小输出级噪声。此外,输出还需匹配网络,通过其在2 GHz频率下谐振,产生一个虚拟的负载电阻。电路中采用TSMC电感为4抽头射频器件,有利于差分结构的对称使用。

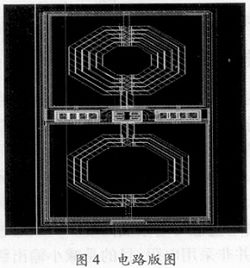

3 版图设计

整体上版图按照对称紧凑进行。同原理图类似,同样是上面布局为输出谐振电感,中间布局为电容和共源共栅放大器以及偏置电路的电阻,为了完全对称,偏置电路电阻采用了两个等值电阻并联,如图1所示。接下来布局为源级电感,最下方布局为偏置电路和电流镜的MOS晶体管,其W相同,只是finger数目不同,这有利于版图的对称和紧凑。版图连线上严格按照电流密度来设定线宽,高频信号线采用135°折线连接,连接孔处尽量采用多孔连接。由于不同的金属层的位置不同以及自身的单位长度上寄生电阻值的差异,因此选用金属层连接需充分考虑以上情况。金属5和金属6寄生电阻值小,且为顶层金属。因此电感和电容采用以上两层金属连接,版图上需尽量使差分输入线的寄生电阻小,LNA版图上充分的加大了线宽和减小连线长度以此减小噪声。

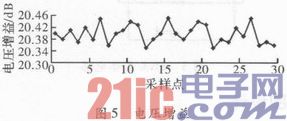

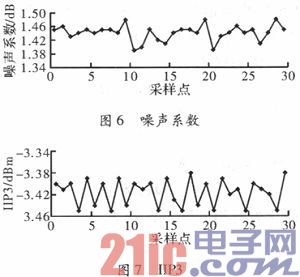

4 芯片测试

电路通过TSMC90nm工艺代工流片。主要测试点有噪声系数、线性度、电压增益等指标。线性度反应的是信号经过低噪声放大后的失真程度。其衡量指标有1 dB压缩点和IIP3 dB压缩点。1 dB压缩点反应的是信号随着强度增加,低噪声放大器对信号非线性放大。IIP3 dB是指信号频率附近的干扰信号同有用信号产生的三阶交条信号对有用信号的干扰程度。采用瞬态测试,输入一个大小为20 mV的2 GHz正弦信号,测试输出正弦信号的大小以测得放大器的增益。取30颗样片分别测试并记录其性能指标,电压增益、噪声系数、IIP3压缩点测试结果分别如下图所示。统计结果分析表明电路的一致性较高,满足应用要求。

5 结束语

文中基于Tsmc0.18μmCMOS工艺,设计了一个全差分的共源共栅低噪声放大器。在电路片内集成电感,在版图上布局。经样片测试结果表明,该电路可获得稳定的输出性能,且一致性高。正常工作条件下,平均电压增益达到20.4 dB,噪声系数为1.44dB,另外IIP3为-3.43 dBm。测试数据证明,该设计具有一定的推广性,可广泛应用于接收机前端放大。

- 音频系统应用中的“POP”噪声以其常用解决方法(12-01)

- 运算放大器电路固有噪声的分析与测量(第二部分):运算放大器噪声介绍(05-12)

- 运算放大器电路固有噪声的分析与测量(第二部分):运算放大器噪声介绍(二)(05-12)

- 运算放大器电路的固有噪声分析与测量(07-14)

- 电源完整性与地弹噪声的高速PCB仿真(05-23)

- 九个步骤大幅降低移动电话非稳态噪声(06-22)