"POP"噪声是指音频器件在上电、断电瞬间以及上电稳定后,各种操作带来的瞬态冲击所产生的爆破声。本文将讨论几种常用的解决方法及其工作原理,这些方法针对具体的集成电路具有各自特点,应用时需要根据实际情况综合考虑。

图1:单端模式与桥式模式输出电路示意图。 本文提到的音频系统是指音频半导体器件,包括音频数模转换器、模数转换器、音频放大器等的应用系统。产生"POP"噪声的瞬态冲击通常是一种很窄的尖脉冲,用傅立叶分析展开后,其频谱分量很丰富,且在频域内的能量分布相对平均。本文下面讨论的几种"POP"噪声解决方法的目的,就是要降低20Hz~20kHz范围内的谐波分量。对绝大多数人而言,如果信号的峰峰值电压小于10mV,就已经听不见了。

桥式(BTL)输出与单端(SE)输出

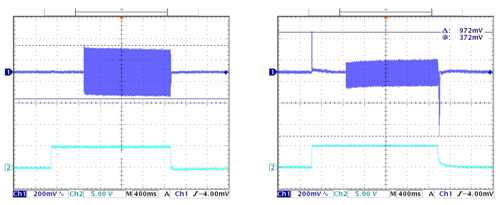

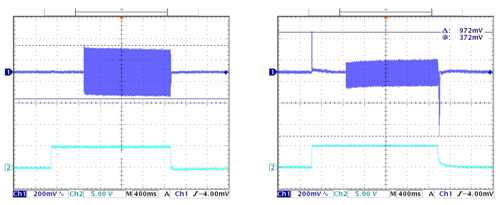

图2:桥式模式与单端模式输出的"POP"噪声。 桥式结构输出相对单端模式输出而言有很多优点,比如桥式模式可在相同的电源电压Vdd条件下,输出较高的电压VOBTL=2*VOSE,在相同的负载条件下输出更大的功率。图1为这两种输出电路的示意图。

需要指出的是,桥式模式能有效抑制共模噪声。输出功率相同时,桥式模式的噪声明显小于单端模式的噪声(如图2所示,蓝色通道接负载两端,绿色通道接电源Vdd)。这是因为相同的冲击会同时出现在桥式输出结构的"+"、"-"两端,并通过负载后相互抵消,不对扬声器做功,因而不会发出"POP"声。这种结构对于上电、掉电噪声以及操作噪声都有很好的抑制作用。

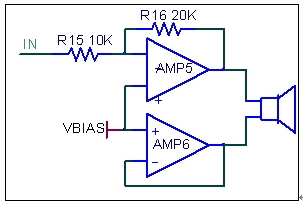

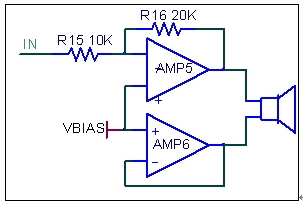

图3:桥式结构的两种电路形式。 常见的桥式结构有两种,它们对抑制"POP"声的能力有细微差别。图3左边的电路是两个放大单元并联连接,同一个输入信号分别进入两个放大单元AMP1、AMP2的"+"、"-"输入端,而且使它们的放大倍数保持相同、相位保持相反(相差180度)。在这里,AMP1单元网络的增益GAINUP=-R9/R8=-2,AMP2单元网络的增益GAINDOWN=1+R11/R12=2。单个电阻的精度误差通常为±30%,但在同一个芯片内,这种偏差朝同一个方向,如果设计恰当,电阻比值的精度可以保证在±1%以内。AMP1、AMP2的DC参数也同样朝同一个方向偏差,所以在"+"、"-"输出端可以很好地抵消共模信号。  图4:OCL输出结构。 图3右边的电路则采用级联形式,前一级的输出信号进入下一级的"-"输入端,AMP4单元网络的增益GAINBACK=-R14/R13=-1。事实上,AMP3的输出经过AMP4反向后会有一定的延时,在"+"、"-"输出端并不能完全抵消。AMP3的失调电压等支流误差信号会在AMP4中复制,并与AMP4的失调电压一起送到"+"端,而无法与"-"端完全抵消。因此这种结构抑制"POP"声的效果略差一些,通常用在小功率器件中。

除此之外,还有一种结构也能有效抑制共模噪声,那就是无输出耦合电容(OCL)结构(见图4)。该结构与桥式结构非常类似,在输出端将直流共模电压抵消掉,只有交流信号对负载作功。与桥式结构一样,OCL结构由于省去了耦合电容,可给音频系统带来另外一个好处,即系统的频率响应可以延伸到很低的范围,后面将对此作详细介绍。

增大VBIAS的滤波电容

图5:单端模式电路的"POP"噪声与Vbias电压的仿真波形。

音频集成电路通常都有一个管脚叫做Vbias,或者Vref、Vmid、Vsvr、bypass等,它是内部直流基准电压,若要内部电路能工作,这个偏置电压必须建立起来。实际应用时,该管脚通常外接一个旁路电解电容到地,该电容起滤除噪声的作用。对于使用正电压的单电源系统来说,当系统工作稳定时,基准电压值约等于Vdd/2。增大这个电容的容值能抑制"POP"噪声。当芯片上电或从待机状态切换到工作状态时,直流偏置电压开始建立,从0逐渐升高,并对Vbias滤波电容充电。经过一定时间后,电压上升到Vdd/2,此时芯片就可以工作了,输出的音频信号基于这个直流电压上下摆动。同样,当芯片掉电或进入待机状态时,滤波电容放电,偏置电压开始下降,从Vdd/2下降到0。实验证明,芯片上电、掉电时的"POP"声就是由偏置电压的瞬间跳变引起的。

图5是仿真结果,红线代表Vbias电压,蓝线代表单端模式的负载端输出(在耦合电容之后,如图1的左边电路,Co=220uF,RL=16Ω)。如果Vbias跳变得缓慢,"POP"冲击就会减小(如图6所示),此时的冲击脉冲变宽,幅度有所下降,"POP"声也变小了。使Vbias的上升、下降过程变缓,就可增加基准电压的跳变延时。假定滤波电容的充放电电流是个常数,可把这个过程简化成一阶RC模型,根据公式(1),可计算出电压从0上升到Vbias/2,或者从Vbias/2下降到0所需的时间。

tdalay=0.69*R*C (1)

| | | | |