超低功耗应用中的高速隔离

时间:10-11

来源:互联网

点击:

作者: Mark Cantrell

在设计师眼中,隔离是一个必不可少的负担。说隔离必不可少,是因为它可以确保电子设备的安全性,使任何人均可使用。说隔离是个负担,是因为它会限制通信速度,会消耗大量电能,并占用电路板空间。基于旧技术的光耦合器,甚至许多较新的数字隔离器能耗巨大,结果使某些类型的应用失去了实用价值。在本文中,我们将考察超低功耗隔离技术的最新发展,及其与现有技术的关系和实现方式。我们还将探讨可从这类新器件中受益的几种应用。

对设计师来说,大约45年前现代光耦合器的出现是一次巨大的飞跃。有了它们,可在电源控制电路中实现反馈,在通信电路中实现信号隔离以断开接地环路,并可实现对高端功率晶体管或电流监控器的通信。20世纪70年代,光电器件大量涌现。这些器件影响了通信标准(如RS232、RS485)和工业总线(如4~20mA电流环路、DeviceNet和Profibus)的发展进程。

受隔离器件本身限制的影响,光隔离的功能决定了这些通信总线的诸多特性。在接下来的20年中,隔离技术的发展变化基本上属于量变,而到了2000年,市场上出现了首批新型芯片级数字隔离器。这些新器件先后采用感性耦合技术、芯片级变压器、GMR材料以及后来的差分容性耦合技术。

这些新技术可以支持比老式光耦合器高得多的速率和低得多的功耗水平,但在既定标准一统天下的情况下,新器件的许多功能(如高速率)并未得到充分利用,因为现有标准接口并没有此项要求。

数字隔离

数字隔离器中的编码和解码电子元件采用标准封装和IC工艺制成,这使得数字功能的添加变得简单易行。低功耗、低电源电压支持以及高集成度已经成为非光学耦合器的主要设计优势。使隔离获得更高速率、更低功耗的创新将支持要求最为苛刻的新接口标准。当前,数字隔离器的功耗虽然显著低于光耦合器,但需要低2至3个数量级才能进入新的应用领域。到目前为止,高性能隔离还不能实现这一目标。

各种技术的比较

隔离器件性能的提升是数据编码方案与数据传输媒介效率共同作用的结果。在本文中,我们将重点讨论决定功耗的各个方面。编码和解码方案大致可以分成基于边沿编码脉冲的系统和电平编码系统两种。最简单的电平系统必须把能量持续地推送通过隔离栅,以保持高电平输出状态,而在不向隔离栅发送能量时则代表低电平输出状态。

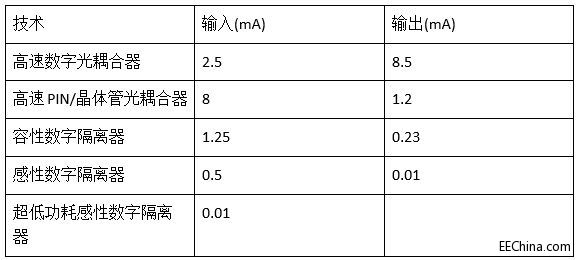

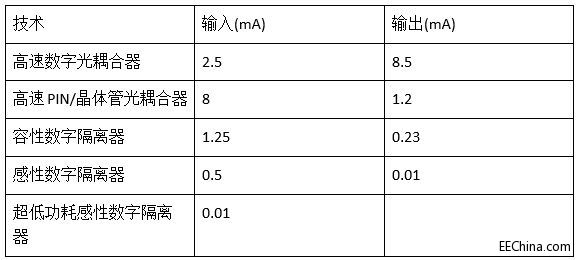

在光耦合器中,能量传输由光促成,与直接形成电场或磁场相比,其效率较差,而且接收元件端的检测效率也差强人意。因此,基于简单晶体管或PIN二极管的光耦合器需消耗大量能量来产生光,以使输出保持开启状态,但接收器接收信号只需消耗很少的能量。这种情况如表1所示,其中展示了PIN二极管接收器光耦合器的功耗。平均而言,高输入电流和低输出电流是这类光耦合器的特点。

表1:隔离器的每通道功耗对比(VDD = 3.3V,100kpbs)

通过为接收器添加有源放大功能,速率较快的数字光耦合器减少了维持某种状态所需光量。虽然这种方法减少了LED的平均电流需求,但接收器的静态电流却相对较大,因此,功耗并未真正降低,只是转移到了接收器端。降低所需功耗就需要提高LED和接收器元件的效率,或者改变编码方案。这也是光耦合器技术在如此长的时期内未取得突破性进展的原因。

容性耦合数字隔离器

在许多容性耦合数字隔离器中,系统实际上类似于光耦合器。这类器件用一个高频振荡器发送信号,使其通过一对差分电容。就像光耦合器的LED一样,该振荡器需要消耗电能以发送高电平状态,关闭以发送低电平状态。接收器配有有源放大器,两种状态下均需消耗偏置电流。如表1所示,得益于电容的高耦合效率,总功耗显著低于光耦合器方案。

需要注意的是,数字隔离器的功率水平大致相当,不管是采用感性耦合还是容性耦合的方案。在这种情况下,决定最低功率水平的主要是编码方案,尤其是在低数据速率条件下。

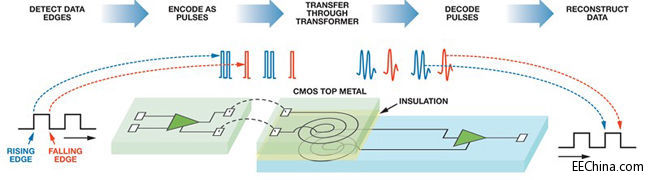

ADI公司基于iCoupler的数字隔离器(如ADuM140x系列)采用另一种编码方案,如图1所示。该方案在输入端检测边沿,并将其编码为脉冲。对于ADuM140x,一个脉冲表示下降沿,两个脉冲表示上升沿。这些脉冲通过片内小型的变压器被耦合到副边。接收器对脉冲计数,重构数据流。脉冲本身非常鲁棒,信噪比出色,但其宽度只有1ns,因此,单位脉冲能量较低。这样造就了一个卓越的属性:无数据变化时,状态在输出端保存于一个锁存器中,几乎不消耗电量。这意味着,功耗就是脉冲流中的集成电能与一些偏置电流之和。随着数据速率的降低,功耗呈线性下降,一直降至直流。同样,实现功耗下降的是编码方案而非特定的数据传输媒介,该方案既可采用容性系统也可采用光学系统。

图1:数字隔离器的脉冲编码方案图示。

Detect data edges: 检测数据边沿

Encode as pulses: 编码为脉冲

Transfer through transformer: 通过变压器耦合

Decode pulses: 解码脉冲

Reconstruct data: 重构数据

Rising edge: 上升沿

Falling edge: 下降沿

CMOS top metal: CMOS顶层金属

Insulation: 隔离

脉冲编码方案并非低功耗的灵丹妙药。其不足在于,如果输入端无逻辑变化,则不会向输出端发送数据。这意味着,如果在上电时序造成输入输出存在不同的直流电平,则输入和输出将不会匹配。ADuM140x解决了这个问题,其方法是在输入通道上设置一个刷新看门狗定时器,如果未检测到活动的时间超过1μs,该定时器将重新发送直流状态。这种设计带来的结果是,当数据速率低于1Mbps时,这种编码方案将不会继续降低功耗。实际上,该器件始终运行于至少1Mbps的数据速率下,因此,在低数据速率情况下,功耗不会继续下降。即便如此,与电平敏感方案相比,脉冲编码方案的平均功耗较低,如表1所示。

在设计师眼中,隔离是一个必不可少的负担。说隔离必不可少,是因为它可以确保电子设备的安全性,使任何人均可使用。说隔离是个负担,是因为它会限制通信速度,会消耗大量电能,并占用电路板空间。基于旧技术的光耦合器,甚至许多较新的数字隔离器能耗巨大,结果使某些类型的应用失去了实用价值。在本文中,我们将考察超低功耗隔离技术的最新发展,及其与现有技术的关系和实现方式。我们还将探讨可从这类新器件中受益的几种应用。

对设计师来说,大约45年前现代光耦合器的出现是一次巨大的飞跃。有了它们,可在电源控制电路中实现反馈,在通信电路中实现信号隔离以断开接地环路,并可实现对高端功率晶体管或电流监控器的通信。20世纪70年代,光电器件大量涌现。这些器件影响了通信标准(如RS232、RS485)和工业总线(如4~20mA电流环路、DeviceNet和Profibus)的发展进程。

受隔离器件本身限制的影响,光隔离的功能决定了这些通信总线的诸多特性。在接下来的20年中,隔离技术的发展变化基本上属于量变,而到了2000年,市场上出现了首批新型芯片级数字隔离器。这些新器件先后采用感性耦合技术、芯片级变压器、GMR材料以及后来的差分容性耦合技术。

这些新技术可以支持比老式光耦合器高得多的速率和低得多的功耗水平,但在既定标准一统天下的情况下,新器件的许多功能(如高速率)并未得到充分利用,因为现有标准接口并没有此项要求。

数字隔离

数字隔离器中的编码和解码电子元件采用标准封装和IC工艺制成,这使得数字功能的添加变得简单易行。低功耗、低电源电压支持以及高集成度已经成为非光学耦合器的主要设计优势。使隔离获得更高速率、更低功耗的创新将支持要求最为苛刻的新接口标准。当前,数字隔离器的功耗虽然显著低于光耦合器,但需要低2至3个数量级才能进入新的应用领域。到目前为止,高性能隔离还不能实现这一目标。

各种技术的比较

隔离器件性能的提升是数据编码方案与数据传输媒介效率共同作用的结果。在本文中,我们将重点讨论决定功耗的各个方面。编码和解码方案大致可以分成基于边沿编码脉冲的系统和电平编码系统两种。最简单的电平系统必须把能量持续地推送通过隔离栅,以保持高电平输出状态,而在不向隔离栅发送能量时则代表低电平输出状态。

在光耦合器中,能量传输由光促成,与直接形成电场或磁场相比,其效率较差,而且接收元件端的检测效率也差强人意。因此,基于简单晶体管或PIN二极管的光耦合器需消耗大量能量来产生光,以使输出保持开启状态,但接收器接收信号只需消耗很少的能量。这种情况如表1所示,其中展示了PIN二极管接收器光耦合器的功耗。平均而言,高输入电流和低输出电流是这类光耦合器的特点。

表1:隔离器的每通道功耗对比(VDD = 3.3V,100kpbs)

通过为接收器添加有源放大功能,速率较快的数字光耦合器减少了维持某种状态所需光量。虽然这种方法减少了LED的平均电流需求,但接收器的静态电流却相对较大,因此,功耗并未真正降低,只是转移到了接收器端。降低所需功耗就需要提高LED和接收器元件的效率,或者改变编码方案。这也是光耦合器技术在如此长的时期内未取得突破性进展的原因。

容性耦合数字隔离器

在许多容性耦合数字隔离器中,系统实际上类似于光耦合器。这类器件用一个高频振荡器发送信号,使其通过一对差分电容。就像光耦合器的LED一样,该振荡器需要消耗电能以发送高电平状态,关闭以发送低电平状态。接收器配有有源放大器,两种状态下均需消耗偏置电流。如表1所示,得益于电容的高耦合效率,总功耗显著低于光耦合器方案。

需要注意的是,数字隔离器的功率水平大致相当,不管是采用感性耦合还是容性耦合的方案。在这种情况下,决定最低功率水平的主要是编码方案,尤其是在低数据速率条件下。

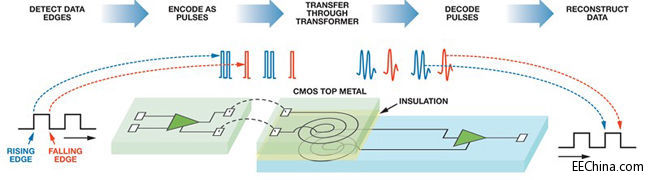

ADI公司基于iCoupler的数字隔离器(如ADuM140x系列)采用另一种编码方案,如图1所示。该方案在输入端检测边沿,并将其编码为脉冲。对于ADuM140x,一个脉冲表示下降沿,两个脉冲表示上升沿。这些脉冲通过片内小型的变压器被耦合到副边。接收器对脉冲计数,重构数据流。脉冲本身非常鲁棒,信噪比出色,但其宽度只有1ns,因此,单位脉冲能量较低。这样造就了一个卓越的属性:无数据变化时,状态在输出端保存于一个锁存器中,几乎不消耗电量。这意味着,功耗就是脉冲流中的集成电能与一些偏置电流之和。随着数据速率的降低,功耗呈线性下降,一直降至直流。同样,实现功耗下降的是编码方案而非特定的数据传输媒介,该方案既可采用容性系统也可采用光学系统。

图1:数字隔离器的脉冲编码方案图示。

Detect data edges: 检测数据边沿

Encode as pulses: 编码为脉冲

Transfer through transformer: 通过变压器耦合

Decode pulses: 解码脉冲

Reconstruct data: 重构数据

Rising edge: 上升沿

Falling edge: 下降沿

CMOS top metal: CMOS顶层金属

Insulation: 隔离

脉冲编码方案并非低功耗的灵丹妙药。其不足在于,如果输入端无逻辑变化,则不会向输出端发送数据。这意味着,如果在上电时序造成输入输出存在不同的直流电平,则输入和输出将不会匹配。ADuM140x解决了这个问题,其方法是在输入通道上设置一个刷新看门狗定时器,如果未检测到活动的时间超过1μs,该定时器将重新发送直流状态。这种设计带来的结果是,当数据速率低于1Mbps时,这种编码方案将不会继续降低功耗。实际上,该器件始终运行于至少1Mbps的数据速率下,因此,在低数据速率情况下,功耗不会继续下降。即便如此,与电平敏感方案相比,脉冲编码方案的平均功耗较低,如表1所示。

电子 电路 电流 总线 变压器 电压 二极管 LED 振荡器 电容 放大器 ADI CMOS 看门狗 传感器 ADC 电阻 相关文章:

- 电力电子装置控制系统的DSP设计方案(04-08)

- DSP和FPGA在汽车电子中的广泛应用 (04-08)

- 基于电力电子应用平台DSP通用板的设计 (04-26)

- μC/OS-II实时操作系统在混合动力整车控制器中的应用(05-22)

- 嵌入式实时操作系统设计及应用探讨(05-25)

- 基于TMS320VC5509A的超声波电子笔设计(06-11)