如何确定嵌入式设计可接受的抖动水平

时间:04-15

来源:互联网

点击:

一个流程图让你步入正轨

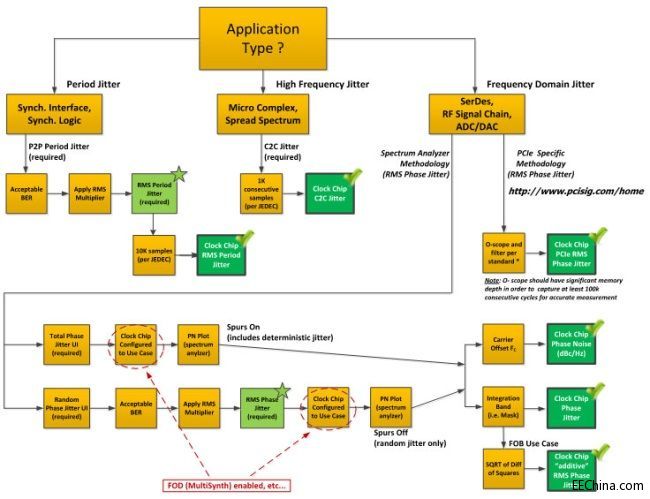

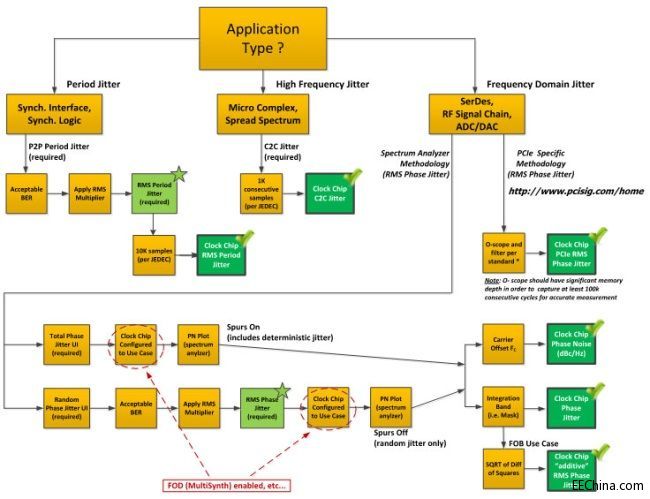

图6中所示的流程图旨在针对具体应用把电路板设计人员引导到正确的抖动规格指标,从而正确地选择时钟芯片。

图6:流程图有助于针对您的应用来确定正确的抖动。

首先要确定应用类型。它是一个同步接口或同步逻辑设计、一个微处理器参考时钟规格指标或扩频时钟、一个高速串行通信或串行/解串器设计?在许多电路板设计中,往往所有这些应用类型都需要进行处理,而且它们都有不同的抖动要求。

对于同步接口或同步逻辑设计,所涉及的应该是周期抖动。你是从P2P周期抖动规格指标开始工作吗?如果是这样,那么你需要确定两个关键限定:首先,按照JEDEC(电子器件工程联合委员会),你在使用的芯片P2P周期抖动是基于10K样本大小。其次,芯片供应商为您提供针对他们规格指标的假定BER。有了这两个限定,就可以得出一个相应的RMS周期抖动规格指标以便选择适当的时钟器件。

如果它是一个消费类电子产品的应用来实现扩频,那么你可能需要使用相邻周期抖动规格指标。按照JEDEC标准,假定相邻周期抖动是在跨越连续1000个周期进行测定。你需要确认是不是这种情况,之后你会有一个有效的相邻周期抖动规格指标来确定相应的时钟芯片。

如果它是一个高速串行通信设计,那么你应该首先询问是否串行标准采用了传统的扩展频谱分析仪方法来量化相位噪声。此外,重要的是要注意PHY厂商针对规格指标到底提供了什么,是P2P总抖动UI,还是P2P随机抖动UI?

需要记住的是RMS只针对于随机抖动,需要将随机抖动要求被BER乘数相除以便得到相应的RMS随机抖动UI。对于随机抖动,你可以使用一个关断杂散的PN曲线,通过积分得到RMS相位抖动值。但是,如果采用一个接通杂散的PN曲线来得到确定性抖动,然后在Mask积分,那么得到的相应值不再是RMS,而是总的相位抖动。

该流程图的目的是针对您的应用引导您通过一个系统化的途径来确定正确的抖动,流程的设计是专门用来避免在本文中详细介绍的常见电路板设计陷阱。

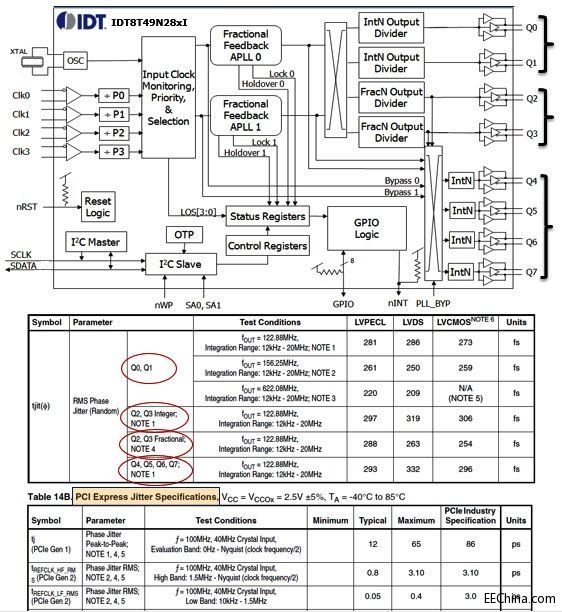

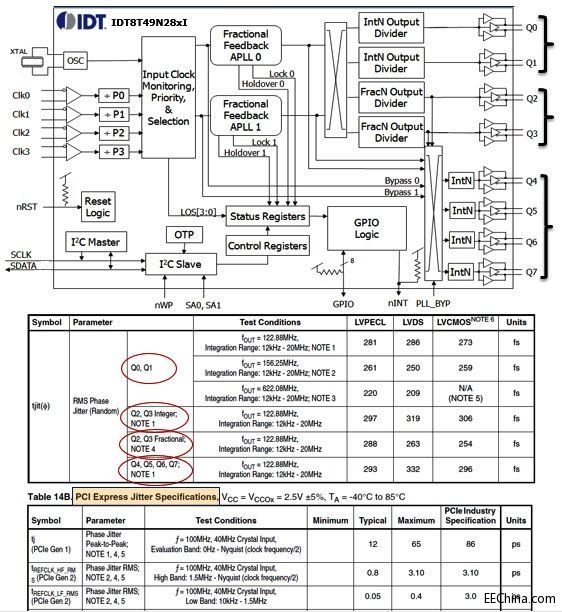

一个有用的时钟器件规格指标应该能够描绘出不同的输出结构和每个结构的相应抖动能力,它还可以针对本文中介绍的不同抖动类型提供规格指标,使设计人员可以为他们的特定应用做好限定。作为一个例子,可以考虑图7中所示的通用频率转换器(UFT)。

图7:IDT8T49N28X通用频率转换器。

这种可配置的时钟器件有几个先进的功能,非常适合于通信线路卡(line-card)应用。它能够以单一器件提供令人印象深刻的高性能(例如低相位噪声)和灵活性。为了实现这种灵活性,该器件采用了一种混合有基于整数和分数的输出分频器,具有为每个输出类型对应的RMS相位抖动差值,详见本器件规格指标。此外,该器件的数据表按照之前提到的PCISIG方法学,以一个单独的表格突出了PCIe相位抖动性能,从而注意到了该串行接口标准中方法学的差异。

重要的是要认识到,一个可配置时钟数据表并不能够覆盖所有的应用案例情况。因此,鼓励设计人员针对特定的应用案例去寻求相应的抖动性能,因为其结果可能略有不同。

作者介绍:

Dean Smith是IDT公司的高级现场应用工程师,他拥有罗彻斯特理工学院(Rochester Institute of Technology)的电子工程学士(BSEE)学位。通过电子邮件dean.smith@idt.com可与Dean Smith联系。

图6中所示的流程图旨在针对具体应用把电路板设计人员引导到正确的抖动规格指标,从而正确地选择时钟芯片。

图6:流程图有助于针对您的应用来确定正确的抖动。

首先要确定应用类型。它是一个同步接口或同步逻辑设计、一个微处理器参考时钟规格指标或扩频时钟、一个高速串行通信或串行/解串器设计?在许多电路板设计中,往往所有这些应用类型都需要进行处理,而且它们都有不同的抖动要求。

对于同步接口或同步逻辑设计,所涉及的应该是周期抖动。你是从P2P周期抖动规格指标开始工作吗?如果是这样,那么你需要确定两个关键限定:首先,按照JEDEC(电子器件工程联合委员会),你在使用的芯片P2P周期抖动是基于10K样本大小。其次,芯片供应商为您提供针对他们规格指标的假定BER。有了这两个限定,就可以得出一个相应的RMS周期抖动规格指标以便选择适当的时钟器件。

如果它是一个消费类电子产品的应用来实现扩频,那么你可能需要使用相邻周期抖动规格指标。按照JEDEC标准,假定相邻周期抖动是在跨越连续1000个周期进行测定。你需要确认是不是这种情况,之后你会有一个有效的相邻周期抖动规格指标来确定相应的时钟芯片。

如果它是一个高速串行通信设计,那么你应该首先询问是否串行标准采用了传统的扩展频谱分析仪方法来量化相位噪声。此外,重要的是要注意PHY厂商针对规格指标到底提供了什么,是P2P总抖动UI,还是P2P随机抖动UI?

需要记住的是RMS只针对于随机抖动,需要将随机抖动要求被BER乘数相除以便得到相应的RMS随机抖动UI。对于随机抖动,你可以使用一个关断杂散的PN曲线,通过积分得到RMS相位抖动值。但是,如果采用一个接通杂散的PN曲线来得到确定性抖动,然后在Mask积分,那么得到的相应值不再是RMS,而是总的相位抖动。

该流程图的目的是针对您的应用引导您通过一个系统化的途径来确定正确的抖动,流程的设计是专门用来避免在本文中详细介绍的常见电路板设计陷阱。

一个有用的时钟器件规格指标应该能够描绘出不同的输出结构和每个结构的相应抖动能力,它还可以针对本文中介绍的不同抖动类型提供规格指标,使设计人员可以为他们的特定应用做好限定。作为一个例子,可以考虑图7中所示的通用频率转换器(UFT)。

图7:IDT8T49N28X通用频率转换器。

这种可配置的时钟器件有几个先进的功能,非常适合于通信线路卡(line-card)应用。它能够以单一器件提供令人印象深刻的高性能(例如低相位噪声)和灵活性。为了实现这种灵活性,该器件采用了一种混合有基于整数和分数的输出分频器,具有为每个输出类型对应的RMS相位抖动差值,详见本器件规格指标。此外,该器件的数据表按照之前提到的PCISIG方法学,以一个单独的表格突出了PCIe相位抖动性能,从而注意到了该串行接口标准中方法学的差异。

重要的是要认识到,一个可配置时钟数据表并不能够覆盖所有的应用案例情况。因此,鼓励设计人员针对特定的应用案例去寻求相应的抖动性能,因为其结果可能略有不同。

作者介绍:

Dean Smith是IDT公司的高级现场应用工程师,他拥有罗彻斯特理工学院(Rochester Institute of Technology)的电子工程学士(BSEE)学位。通过电子邮件dean.smith@idt.com可与Dean Smith联系。

电路 FPGA 仿真 电子 频谱分析仪 滤波器 低通滤波器 示波器 开关电源 IDT 相关文章:

- DSP外围电路(10-09)

- TMS32OF2812与DIP-IPM的通用电路设计(07-31)

- TMS320F206外围电路典型设计 (04-17)

- 基于DSP芯片TMS320LF2407A的超声电源系统的控制电路(08-01)

- 多片DDC芯片HSP50214B与DSP接口电路设计(08-21)

- DSP电源系统的低功耗设计(11-13)