TMS320F206外围电路典型设计

1 引 言

数字信号处理DSP芯片是一种能够实时快速地实现各种数字信号处理算法控制的微处理器,已经在通信与信息系统、信号与处理、自动控制、雷达、航空航天、医疗等许多领域得到了广泛的应用。

目前生产DSF 芯片的厂家主要有TI公司、AD公司、Motorola公司等。其中TI公司推出的 TMS320C2xx系列是继TMS320C2x和TMA320C5x之后的一种低价格、高性能16位定点运算DSP。TMS320F206(以下简称F206)是2xx系列的代表之一,性价比高,应用广泛,目前已成为高档单片机的理想替代。F206的性能特点如下:

(1)指令周期可达25 ns;

(2)可寻址64 kB程序空间、64 kB数据空间、64 kB I/O空间以及32 kB全局存储空间;

(3)片内集成有32 kB FLASH存储器;

(4)32位算术逻辑单元、32位累加器、16位并行乘法器;

(5)丰富的片内外设,可编程等待状态发生器、锁相环、同步串行口、异步串行口等;

(6)与IEEE标准1149.1兼容的JTAG串行逻辑扫描电路。

DSP芯片外围电路设计是用好DSP芯片最关键的第一步。本文以TMS320F206为例介绍DSP芯片前向通道、后向通道接口电路,外存存储器扩展等最为典型的设计思路及方法。

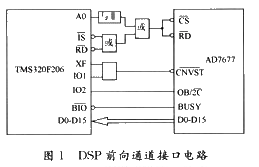

2 F206前向通道接口

AD7677芯片是AD公司新推出的具有1 MSPS(Mega Sample Per Second)16位模数转换芯片。该芯片采用开关电容式逐次比较结构,其内部自带采样保持器(SHA)、时钟源、+2.5 V参考电压、误差修正电路、差分输人以及并行/串行输出接口。采用单+5 V电源供电,正常工作情况下的功耗为115 mW;关闭模式下的功耗仅为7μW。具有高达94 dB的优越的动态范围,积分非线性(INI)最大为±O.5 LSB,无漏码差分非线性(DNL)最大为16位。并具有3种可选工作模式:Warp/Normal/Impulse。

ADC采样的精度取决于参考电压、布线以及正确的时序。对于其中的布线主要是指电源和地、参考电压的抗干扰性能。电源和地的干扰是造成系统误差的最主要原因。

对于许多高性能数据采集应用,为了解决ADC与放大器之间的匹配问题,AD7677 还可与AD公司的AD8021运算放大器配对使用。AD8021是为了解决增益和带宽性能之间的匹配问题的一种定制补偿放大器。

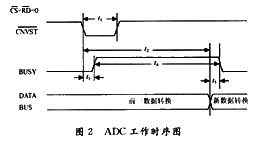

DSP芯片(TMS320F206)工作于20MHz时钟周期。ADC工作于Warp模式,其采样速度达到1MSPS,每两次转换时间间隔不超过1ms ,否则会导致前一转换结果的覆盖丢失。

正常工作状态下,当DSP的地址判断位A0为高,且I/O口空间选择信号IS以及读选择信号RD同时为低时,A/D的片选信号CS及读请求信号RD同时为低。即表示A/D被选中且准备数据转换。由DSP的I/O口触发A/D转换开始信号CNVST(t1),A/D的引脚BUSY保持高(t2),即开始数据的转换。其工作时序如图2所示。

3 F206后向通道接口

单集成芯片AD669是16位高分辨率,40 ns高速转换的数模转换器。

AD669数据锁存采用分段译码结构(Segmented Decoded Architecture),可减少与数码相关的毛刺,同时采用双缓存锁存结构,避免了虚假模拟信号的产生。AD669内部集成隐埋式齐纳基准,10.000 V基准最大误差为±0.2%。另外AD669具有管脚可定义单极(0~10 V)双极性(一10~+l0 V)输出,并可实现增益及零偏调节。

DSP芯片(TMS320F206)工作于20 MHz时钟周期,外挂JTAG仿真口,便于实时烧写、调试程序。DAC工作于边沿触发模式,即LDAC与CS连接在一起,而L1直接接地,两级锁存链接成主从结构。

TMS320F206与AD669接口电路框图如图3所示。

正常工作状态下,当DSP的I/O口空间选择信号IS以及写选择信号WE其中一个由低变高时,则会使D/A的LDAC-CS产生上升沿(tLOWtHIGH),开始同时更新两级锁存中的数据。其工作时序如图4所示。

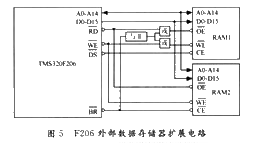

4 F206外部数据存储器扩展

DSP芯片通常需要通过外部存储器来扩展数据存储空间。F206内部集成64 kB数据存储空间,外部数据存储器可以扩展至32 kB空间。为了使存储接口速度快,选用ISSI公司的高速存储器IS61C3216,该数据存储器为32 k×16 b的CMOS静态RAM,其读写访问时间仅为10 ns。

F206芯片的总线请求信号BR以及全局存储器分配寄存器GREG可以把数据存储器扩展至32 kB空间。用两块IS61C3216,一组作为局部数据存储器,一组作为全局数据存储器,地址共用8000h~FFFFh。其扩展电路框图如图5所示。

当GREG=xx00h时,8000h~FFFFh地址区域被配置为局部数据存储器,此时,BR=1,RAM2禁止访问,RAM1两个使能信号打开,选中RAM1;当GREG=xx80h时,8000h~FFFFh被配置为全局数据存储器,此时,BR=0,RAMl被禁止局部数据存储器将不能访问。

通过外部存储器扩展,F206具有64kB的局部数据存储器空间,用来存放指令使用的数据;32 kB的全局

TMS320F206 外围电路 DSP芯片 相关文章:

- 基于TMS320F206 DSP的图像采集卡设计(06-26)

- DSP在心电监护模块中的应用(08-20)

- 基于DSP TMS320F206的仿真调试 (07-06)

- 基于TMS320F206的多协议数据传输 (09-25)

- 基于DSP虚拟I2C总线软件包的设计及应用实例(03-11)

- 基于DSP的DMA控制技术概述(04-17)