如何确定嵌入式设计可接受的抖动水平

时间:04-15

来源:互联网

点击:

芯片厂商的规格指标并不一致

除了许多不同的抖动类型和细微差别,芯片制造商如何为他们的器件确定所需的时钟抖动也有很多的不确定性。 SerDes芯片厂商为他们的元件确定所需的参考时钟抖动,但是物理层、FPGA和处理器等器件规格指标则不一定与行业串行接口标准的方法学和测量细节等保持一致。

例如,大部分网络通信标准(如千兆以太网,10千兆以太网等)指定峰-峰(P2P)值总抖动作为一个单位间隔(UI)的百分比,其中一个UI在给定串行标准中相当于时间域1比特间隔。但是峰-峰值总抖动UI实际上是一个SerDes眼图关闭(eye closure)规格指标,以符合可接受的比特误码率(BER),根据工业串行标准其通常是10-12。

这些标准并没有界定总抖动UI预算有多少被分配给互连、光学、串行解串器,或驱动SerDes的参考时钟。其结果是,电路板设计人员只能听命于芯片供应商以及在他们的数据表中规定的参考时钟抖动。通常,这些规格指标都过于保守,把大多数抖动预算给予了集成的SerDes,为需要驱动SerDes的参考时钟只留下少许。

使问题更加复杂的是,来自时钟芯片厂商的抖动规格指标可能是模糊的,也不一定完整。一些供应商对于时钟产品的描述(specmanship)建立在不适当规格指标和测量结果基础上,通常不适合于目标应用,对于给定的规格指标会产生不一致并缺失关键的限定。

常见的抖动陷阱

对于电路板设计人员来说,有许多容易导致错误的陷阱。本节会扩展来讨论一些下面列出的常见陷阱的更多详细信息:

*P2P随机抖动规格指标没有针对目标应用BER限定

*把针对通信应用而设计的时钟抖动规格指标和方法学应用于PCIe端口

*PN曲线生成时关断杂散波以便满足总相位抖动要求( 通过使用随机RMS相位抖动测量忽略了确定性抖动)

*抖动的测量/确定仅仅是针对器件,而不是针对给定应用(如整数模式下的w/内置 MultiSynth分频器)的案例配置

*添加RMS相位抖动(Additive RMS phase jitter)的测量作为输入和输出抖动之间的简单差值,而不是输入和输出抖动平方差的平方根值

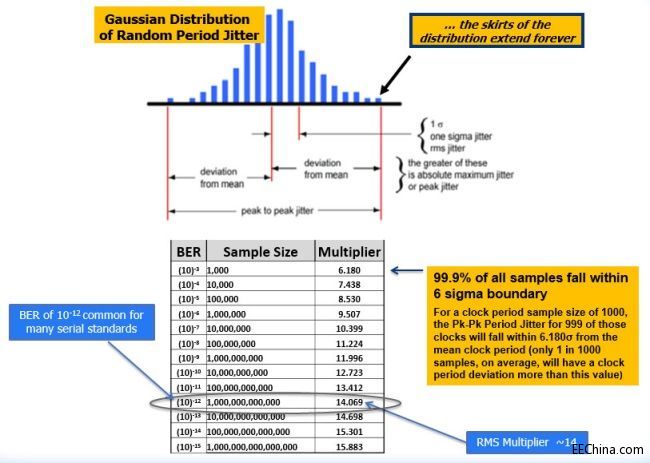

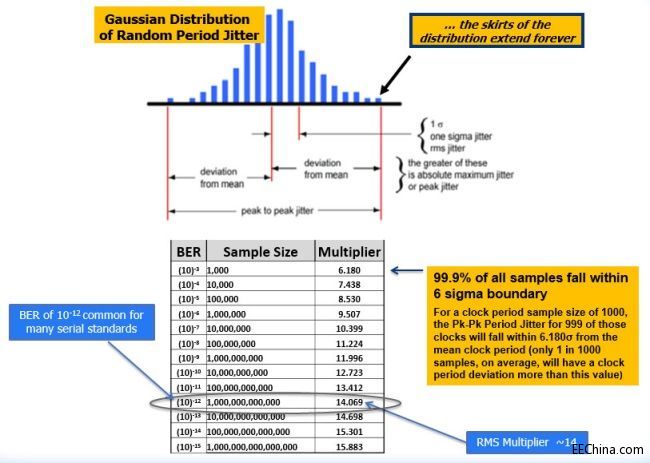

例如,图3所示随机周期抖动的高斯分布裙边会无限延伸下去,这是因为随机抖动没有边界,因此,实际测量P2P周期抖动绝对最大值并不现实。然而,在高斯分布上超过一个点的抖动可以给定一个概率。 BER依特定应用而定,并且通常用于此目的。

图3:随机周期抖动的高斯分布裙边无限延伸。

没有芯片供应商提供的可接受的BER,P2P周期抖动规格指标毫无意义。然而,这个限定往往难以从器件的数据表中看到。对于给定的应用,如果已知道可接受的BER,该给定应用的RMS周期抖动之后可以计算出来。所以,重要的是设计者必须要知道他们应用的正确BER。此外,请注意这种方法不是针对于周期抖动,因为它可用于计算各种类型的RMS抖动。作为例子,一个RMS相位抖动的计算如下所示:

考虑到10GE PHY需要的随机相位抖动UI=0.18 UI

... 因为比特率是10.3125Gbps,1 UI=96.9pS

...假定给定应用可接受的BER是10-12

那么,所需的相应RMS相位抖动的计算公式为:

[(0.18)*(96.9pS)]÷(14.069) = 1.24pS

PCIe已经成为通信应用普遍的控制层面接口,以太网物理层等器件集成PCIe端口用于连接带外的控制层面微处理器(micro)。至少一个著名的以太网PHY厂商已经为他们的PCIe参考时钟确定RMS相位抖动,其方式类似于在同样器件中他们为以太网端口确定RMS相位抖动,通过由频谱分析仪所产生的相位噪声曲线进行有效地外延。但是,这种方式不符合PCIe标准抖动方法,如图4中可详细说明。

图4: 针对PCIe标准测量参考时钟抖动的7个步骤。

按照PCIe标准测量参考时钟抖动的基本步骤如下:

(假定为常见模式时钟)

1) 用示波器(高取样率)得到所测周期时间的初始数据记录

2) 通过每个数据点减去平均值来计算针对每个周期的‘周期误差’

3) 通过对每个周期的周期误差进行累积求和,从而转化为‘相位误差’

……得到您的有效‘初始’相位误差

4) 通过快速傅里叶变换(FFT)转变到频域

5) 把特定的遮罩(mask)应用于感兴趣的标准,Gen1,Gen2,或者Gen3

6) 进行快速傅里叶逆变换(iFFT)操作再变换到时域

……得到‘过滤的’相位误差

7) 根据适当的标准误码率(BER)要求把RMS相位抖动转换为峰值到峰值抖动

……10-12误码率,通过RMS的14X乘法器得到相应的峰值到峰值抖动

相反,PCIe方法是采用示波器测量得到的原始周期样本,然后应用FFT、滤波器和iFFT步骤来得出适当的RMS相位抖动测量。重要的是要注意到这两种不同的方法可以产生完全不同的结果。

因此,设计人员可能会误认为设计的时钟器件达到或超过了PCIe参考时钟抖动规格指标或者标准,但是这些器件却不足以驱动PCIe端口,原因是这些PHY厂家采用了不同的方法和/或过滤器来确定所需的参考时钟抖动。

如先前所讨论的,P2P总抖动(UI)是特定于SerDes的数据信号。这包括确定性和随机抖动对于数据信号眼图的贡献。人们普遍认为,在SerDes链路的确定性抖动很大程度上与链路本身和其他系统障碍有关。

随机抖动主要可归因于SerDes外部参考时钟和SerDes内部的PLL。但我们知道,参考时钟也具有一定量的确定性抖动。此外,许多PHY供应商的数据表并没有区分列出驱动他们SerDes参考时钟的随机与确定性抖动要求。由于这些原因,另一种常见的设计陷阱是使用PN曲线来量化时钟器件的总相位抖动,其中包括确定性抖动,但杂散被关断 (杂散是“周期性杂散噪声”的简写,代表了时钟的确定性抖动)。此确定性抖动可来源于电路板设计本身和/或时钟芯片,串扰、电磁干扰(EMI)、开关电源噪声、和PLL小数反馈分频器都可以是这种确定性抖动的来源。

对于图5中所示的PN曲线例子,其特殊的电路板设计使在PLL输出端测得显著的杂散内容。不幸的是,这些杂散噪声处在该应用感兴趣的12kHz至20MHz积分范围内。因此,参考时钟的总相位抖动已经超出了SerDes芯片供应商的规格指标,结果是较高的BER。采用EMI嗅探器(sniffer)分析这些问题的根本原因,发现这种杂散的内容可追溯到用于给PLL供电的同步降压开关稳压器,通过电路板布局修改和无源元件的变化可以减轻这一问题。

图5:具有杂散噪声的 PN曲线示例。

然而,某些杂散内容来自PLL时钟器件本身。重要的是要记住,任何时钟合成器可以产生许多不需要的和与差频率,它们的强度可能很大足以显著出现在PN曲线上。

当今优秀的PLL设计都采用先进的硅设计技术。这些进展有助于减少内在产生的随机和确定性(杂散)抖动。但对于抖动关键的板载时钟,设计师需要义不容辞地与定时器件厂商验证给定的时钟器件其相应的相位抖动规格指标是基于杂散导通时得到的PN曲线。

除了许多不同的抖动类型和细微差别,芯片制造商如何为他们的器件确定所需的时钟抖动也有很多的不确定性。 SerDes芯片厂商为他们的元件确定所需的参考时钟抖动,但是物理层、FPGA和处理器等器件规格指标则不一定与行业串行接口标准的方法学和测量细节等保持一致。

例如,大部分网络通信标准(如千兆以太网,10千兆以太网等)指定峰-峰(P2P)值总抖动作为一个单位间隔(UI)的百分比,其中一个UI在给定串行标准中相当于时间域1比特间隔。但是峰-峰值总抖动UI实际上是一个SerDes眼图关闭(eye closure)规格指标,以符合可接受的比特误码率(BER),根据工业串行标准其通常是10-12。

这些标准并没有界定总抖动UI预算有多少被分配给互连、光学、串行解串器,或驱动SerDes的参考时钟。其结果是,电路板设计人员只能听命于芯片供应商以及在他们的数据表中规定的参考时钟抖动。通常,这些规格指标都过于保守,把大多数抖动预算给予了集成的SerDes,为需要驱动SerDes的参考时钟只留下少许。

使问题更加复杂的是,来自时钟芯片厂商的抖动规格指标可能是模糊的,也不一定完整。一些供应商对于时钟产品的描述(specmanship)建立在不适当规格指标和测量结果基础上,通常不适合于目标应用,对于给定的规格指标会产生不一致并缺失关键的限定。

常见的抖动陷阱

对于电路板设计人员来说,有许多容易导致错误的陷阱。本节会扩展来讨论一些下面列出的常见陷阱的更多详细信息:

*P2P随机抖动规格指标没有针对目标应用BER限定

*把针对通信应用而设计的时钟抖动规格指标和方法学应用于PCIe端口

*PN曲线生成时关断杂散波以便满足总相位抖动要求( 通过使用随机RMS相位抖动测量忽略了确定性抖动)

*抖动的测量/确定仅仅是针对器件,而不是针对给定应用(如整数模式下的w/内置 MultiSynth分频器)的案例配置

*添加RMS相位抖动(Additive RMS phase jitter)的测量作为输入和输出抖动之间的简单差值,而不是输入和输出抖动平方差的平方根值

例如,图3所示随机周期抖动的高斯分布裙边会无限延伸下去,这是因为随机抖动没有边界,因此,实际测量P2P周期抖动绝对最大值并不现实。然而,在高斯分布上超过一个点的抖动可以给定一个概率。 BER依特定应用而定,并且通常用于此目的。

图3:随机周期抖动的高斯分布裙边无限延伸。

没有芯片供应商提供的可接受的BER,P2P周期抖动规格指标毫无意义。然而,这个限定往往难以从器件的数据表中看到。对于给定的应用,如果已知道可接受的BER,该给定应用的RMS周期抖动之后可以计算出来。所以,重要的是设计者必须要知道他们应用的正确BER。此外,请注意这种方法不是针对于周期抖动,因为它可用于计算各种类型的RMS抖动。作为例子,一个RMS相位抖动的计算如下所示:

考虑到10GE PHY需要的随机相位抖动UI=0.18 UI

... 因为比特率是10.3125Gbps,1 UI=96.9pS

...假定给定应用可接受的BER是10-12

那么,所需的相应RMS相位抖动的计算公式为:

[(0.18)*(96.9pS)]÷(14.069) = 1.24pS

PCIe已经成为通信应用普遍的控制层面接口,以太网物理层等器件集成PCIe端口用于连接带外的控制层面微处理器(micro)。至少一个著名的以太网PHY厂商已经为他们的PCIe参考时钟确定RMS相位抖动,其方式类似于在同样器件中他们为以太网端口确定RMS相位抖动,通过由频谱分析仪所产生的相位噪声曲线进行有效地外延。但是,这种方式不符合PCIe标准抖动方法,如图4中可详细说明。

图4: 针对PCIe标准测量参考时钟抖动的7个步骤。

按照PCIe标准测量参考时钟抖动的基本步骤如下:

(假定为常见模式时钟)

1) 用示波器(高取样率)得到所测周期时间的初始数据记录

2) 通过每个数据点减去平均值来计算针对每个周期的‘周期误差’

3) 通过对每个周期的周期误差进行累积求和,从而转化为‘相位误差’

……得到您的有效‘初始’相位误差

4) 通过快速傅里叶变换(FFT)转变到频域

5) 把特定的遮罩(mask)应用于感兴趣的标准,Gen1,Gen2,或者Gen3

6) 进行快速傅里叶逆变换(iFFT)操作再变换到时域

……得到‘过滤的’相位误差

7) 根据适当的标准误码率(BER)要求把RMS相位抖动转换为峰值到峰值抖动

……10-12误码率,通过RMS的14X乘法器得到相应的峰值到峰值抖动

相反,PCIe方法是采用示波器测量得到的原始周期样本,然后应用FFT、滤波器和iFFT步骤来得出适当的RMS相位抖动测量。重要的是要注意到这两种不同的方法可以产生完全不同的结果。

因此,设计人员可能会误认为设计的时钟器件达到或超过了PCIe参考时钟抖动规格指标或者标准,但是这些器件却不足以驱动PCIe端口,原因是这些PHY厂家采用了不同的方法和/或过滤器来确定所需的参考时钟抖动。

如先前所讨论的,P2P总抖动(UI)是特定于SerDes的数据信号。这包括确定性和随机抖动对于数据信号眼图的贡献。人们普遍认为,在SerDes链路的确定性抖动很大程度上与链路本身和其他系统障碍有关。

随机抖动主要可归因于SerDes外部参考时钟和SerDes内部的PLL。但我们知道,参考时钟也具有一定量的确定性抖动。此外,许多PHY供应商的数据表并没有区分列出驱动他们SerDes参考时钟的随机与确定性抖动要求。由于这些原因,另一种常见的设计陷阱是使用PN曲线来量化时钟器件的总相位抖动,其中包括确定性抖动,但杂散被关断 (杂散是“周期性杂散噪声”的简写,代表了时钟的确定性抖动)。此确定性抖动可来源于电路板设计本身和/或时钟芯片,串扰、电磁干扰(EMI)、开关电源噪声、和PLL小数反馈分频器都可以是这种确定性抖动的来源。

对于图5中所示的PN曲线例子,其特殊的电路板设计使在PLL输出端测得显著的杂散内容。不幸的是,这些杂散噪声处在该应用感兴趣的12kHz至20MHz积分范围内。因此,参考时钟的总相位抖动已经超出了SerDes芯片供应商的规格指标,结果是较高的BER。采用EMI嗅探器(sniffer)分析这些问题的根本原因,发现这种杂散的内容可追溯到用于给PLL供电的同步降压开关稳压器,通过电路板布局修改和无源元件的变化可以减轻这一问题。

图5:具有杂散噪声的 PN曲线示例。

然而,某些杂散内容来自PLL时钟器件本身。重要的是要记住,任何时钟合成器可以产生许多不需要的和与差频率,它们的强度可能很大足以显著出现在PN曲线上。

当今优秀的PLL设计都采用先进的硅设计技术。这些进展有助于减少内在产生的随机和确定性(杂散)抖动。但对于抖动关键的板载时钟,设计师需要义不容辞地与定时器件厂商验证给定的时钟器件其相应的相位抖动规格指标是基于杂散导通时得到的PN曲线。

电路 FPGA 仿真 电子 频谱分析仪 滤波器 低通滤波器 示波器 开关电源 IDT 相关文章:

- DSP外围电路(10-09)

- TMS32OF2812与DIP-IPM的通用电路设计(07-31)

- TMS320F206外围电路典型设计 (04-17)

- 基于DSP芯片TMS320LF2407A的超声电源系统的控制电路(08-01)

- 多片DDC芯片HSP50214B与DSP接口电路设计(08-21)

- DSP电源系统的低功耗设计(11-13)