藏在系统核心芯片中的DRAM控制器

时间:12-10

来源:互联网

点击:

建立一个控制器

与前面所述不同的是DRAM时序非常复杂,接近混沌。从DRAM芯片设计人员的角度看,这非常合理,但是,很难满足多核SoC的需求。DRAM序列或者时序命令上看起来无关紧要的小改动会导致您访问存储器的带宽的巨大变化。由于存储器带宽通常是关键任务的瓶颈所在,因此,带宽的变化很快就会影响系统性能。然而,命令序列和时序来自应用程序和系统软件之间,以及系统硬件各种单元之间复杂的交互——包括缓存控制器、存储器管理器、直接存储器访问(DMA)控制器和加速器,以及DRAM控制器。

SoC的功能越来越强大,这种情况会更加复杂。目前,一个多核系统级IC会有同时运行的两个甚至更多的多线程CPU,导致共享L2高速缓存来读取指令线,随机对数据线进行读写操作。同时,计算加速器以自己的方式遍历数据结构。一个器件可以处理流视频,另一个用于矩阵乘法预读取,第三个执行路由表的随机访问。增加一个散射收集DMA控制器,处理光纤接口、硬盘和显示器之间的数据,结果是,在DRAM控制器的系统侧会有些不协调。

如果DRAM控制器只是按照系统接收顺序进行操作,那么,优化DRAM操作的工作会同等落在规划人员、设计人员和软件开发人员上——这是很难做到的。Altera公司战略市场经理Argy Krikelis提醒说:“特别是多核设计,规划人员遇到定位和性能问题。”责任落在DRAM控制器上,那么,尽可能利用其信息消除这种不协调,转换为经过优化的命令流。

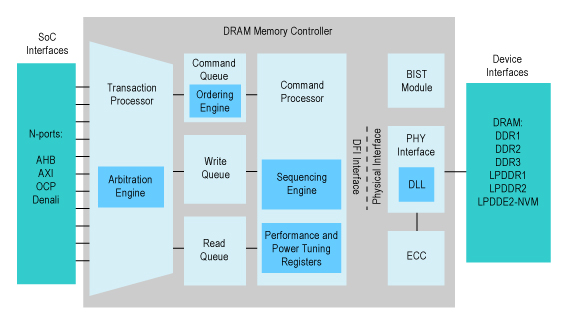

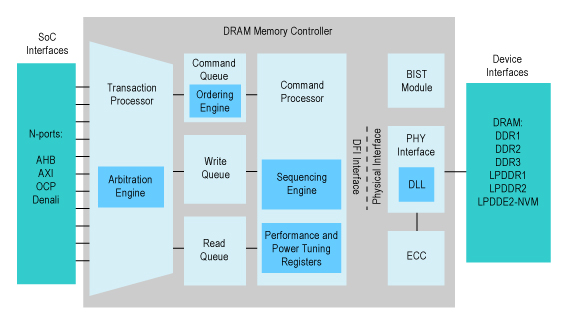

深入了解DRAM控制器就会知道,这些模块的设计人员怎样处理这些难题。您可以认为一个现代DRAM控制器有三个主要模块——物理接口、命令处理器以及事物处理器——如图3 所示。

图3.一个现代DRAM控制器涉及到事物处理器、命令处理器和物理接口。

物理接口连接DRAM芯片或者存储器模块。它读取来自命令处理器的一个命令流,将具有正确时序的命令发送至DRAM芯片,管理相关的数据字节流。接口收发器、命令和数据同步缓冲,以及产生正确命令和数据时序的状态机都含在这一模块中。而且,还有用于进行复杂的初始化操作的状态机,校准DDR3 DRAM规范设定的序列,如图1所示。此外,某些应用的物理接口还会包括自测试、诊断和误码探测以及纠错硬件。当您改变DRAM的容量或者速率等级时,必须调整物理接口。

物理接口的上游是命令处理器。这一模块跟踪DRAM的状态,将到达总线读写周期转换为相应的DRAM命令序列。例如,命令处理器会找到通过其输入队列散射连续字的总线读序列,然后,向其输出队列发出预充电,激活,以及模块读命令。对此,命令处理器必须知道当发出新命令后,将打开哪一芯片的哪一块的哪一行。在某些设计中,命令处理器还处理地址重新映射,在多个块上扩展一个连续的数据结构。

随着对带宽需求的增长,命令处理器的复杂度也在不断提高。例如,处理器会提前处理其输入队列,重新安排操作,尽可能保持在激活的行上,重叠预充电读操作,或者对块进行间插操作。最重要的是,处理器会尽量避免一个块的行之间出现乒乓效应。必须确定所有这些调整,并且随时能够进行调整。 这方面的努力会有其回报。Krikelis说:“我们看到在某些应用中,分组和重新排序能够实现92%的理论最大DRAM带宽。”

最后,事物处理器位于命令处理器和SoC的其他部分之间。一般有一些通道连接至SoC的高速中心交换结构上。事物处理器的主要工作是将到达的各种通道的读写数据流进行组合,加上优先级,这样,每一通道得到了所需的延时和带宽——因此,每一高速缓存控制器、DMA引擎或者这些通道另一端的加速器也得到了所需的延时和带宽。

在动态环境中选择这种优先级方案并不容易。如果您不能精确的预测每一通道的数据流特性,那么,这会非常困难。理想情况下,工作负荷是固定的,因此,您可以为其优化优先级方案。或者,会有一些清晰的访问模式,随着数据流的变化而提供动态调整优先级。Krikelis说,系统规划人员和控制器设计人员研究了这一问题,使用了从表格到商用DRAM仿真工具的所有工具。但,还是无法让工作更简单一些。

在某些情况下,应用的特征很明显,事物处理器会承担更多的工作。Krikelis说,可以对最近的DRAM行进行高速缓存操作,或者控制器中经常被激活的行进行高速缓存操作。而且,在某些情况下,设计人员可以针对某些通道进行一些特定任务的重新排序或者某些读写操作。

高级DRAM控制器中的三个主要模块协同工作,能够使复杂多核SoC尽可能接近最大理论DRAM带宽。但是提高带宽可能需要牺牲延时,最高优先级线程除外。某些控制器设计会有32或者64深命令序列,意味着,低优先级访问会长时间停留在序列中。一般而言,DRAM控制器能够进行的工作越多,它处理的SoC体系结构和组合任务就越具体。这就把难题留给了系统设计人员。

与前面所述不同的是DRAM时序非常复杂,接近混沌。从DRAM芯片设计人员的角度看,这非常合理,但是,很难满足多核SoC的需求。DRAM序列或者时序命令上看起来无关紧要的小改动会导致您访问存储器的带宽的巨大变化。由于存储器带宽通常是关键任务的瓶颈所在,因此,带宽的变化很快就会影响系统性能。然而,命令序列和时序来自应用程序和系统软件之间,以及系统硬件各种单元之间复杂的交互——包括缓存控制器、存储器管理器、直接存储器访问(DMA)控制器和加速器,以及DRAM控制器。

SoC的功能越来越强大,这种情况会更加复杂。目前,一个多核系统级IC会有同时运行的两个甚至更多的多线程CPU,导致共享L2高速缓存来读取指令线,随机对数据线进行读写操作。同时,计算加速器以自己的方式遍历数据结构。一个器件可以处理流视频,另一个用于矩阵乘法预读取,第三个执行路由表的随机访问。增加一个散射收集DMA控制器,处理光纤接口、硬盘和显示器之间的数据,结果是,在DRAM控制器的系统侧会有些不协调。

如果DRAM控制器只是按照系统接收顺序进行操作,那么,优化DRAM操作的工作会同等落在规划人员、设计人员和软件开发人员上——这是很难做到的。Altera公司战略市场经理Argy Krikelis提醒说:“特别是多核设计,规划人员遇到定位和性能问题。”责任落在DRAM控制器上,那么,尽可能利用其信息消除这种不协调,转换为经过优化的命令流。

深入了解DRAM控制器就会知道,这些模块的设计人员怎样处理这些难题。您可以认为一个现代DRAM控制器有三个主要模块——物理接口、命令处理器以及事物处理器——如图3 所示。

图3.一个现代DRAM控制器涉及到事物处理器、命令处理器和物理接口。

物理接口连接DRAM芯片或者存储器模块。它读取来自命令处理器的一个命令流,将具有正确时序的命令发送至DRAM芯片,管理相关的数据字节流。接口收发器、命令和数据同步缓冲,以及产生正确命令和数据时序的状态机都含在这一模块中。而且,还有用于进行复杂的初始化操作的状态机,校准DDR3 DRAM规范设定的序列,如图1所示。此外,某些应用的物理接口还会包括自测试、诊断和误码探测以及纠错硬件。当您改变DRAM的容量或者速率等级时,必须调整物理接口。

物理接口的上游是命令处理器。这一模块跟踪DRAM的状态,将到达总线读写周期转换为相应的DRAM命令序列。例如,命令处理器会找到通过其输入队列散射连续字的总线读序列,然后,向其输出队列发出预充电,激活,以及模块读命令。对此,命令处理器必须知道当发出新命令后,将打开哪一芯片的哪一块的哪一行。在某些设计中,命令处理器还处理地址重新映射,在多个块上扩展一个连续的数据结构。

随着对带宽需求的增长,命令处理器的复杂度也在不断提高。例如,处理器会提前处理其输入队列,重新安排操作,尽可能保持在激活的行上,重叠预充电读操作,或者对块进行间插操作。最重要的是,处理器会尽量避免一个块的行之间出现乒乓效应。必须确定所有这些调整,并且随时能够进行调整。 这方面的努力会有其回报。Krikelis说:“我们看到在某些应用中,分组和重新排序能够实现92%的理论最大DRAM带宽。”

最后,事物处理器位于命令处理器和SoC的其他部分之间。一般有一些通道连接至SoC的高速中心交换结构上。事物处理器的主要工作是将到达的各种通道的读写数据流进行组合,加上优先级,这样,每一通道得到了所需的延时和带宽——因此,每一高速缓存控制器、DMA引擎或者这些通道另一端的加速器也得到了所需的延时和带宽。

在动态环境中选择这种优先级方案并不容易。如果您不能精确的预测每一通道的数据流特性,那么,这会非常困难。理想情况下,工作负荷是固定的,因此,您可以为其优化优先级方案。或者,会有一些清晰的访问模式,随着数据流的变化而提供动态调整优先级。Krikelis说,系统规划人员和控制器设计人员研究了这一问题,使用了从表格到商用DRAM仿真工具的所有工具。但,还是无法让工作更简单一些。

在某些情况下,应用的特征很明显,事物处理器会承担更多的工作。Krikelis说,可以对最近的DRAM行进行高速缓存操作,或者控制器中经常被激活的行进行高速缓存操作。而且,在某些情况下,设计人员可以针对某些通道进行一些特定任务的重新排序或者某些读写操作。

高级DRAM控制器中的三个主要模块协同工作,能够使复杂多核SoC尽可能接近最大理论DRAM带宽。但是提高带宽可能需要牺牲延时,最高优先级线程除外。某些控制器设计会有32或者64深命令序列,意味着,低优先级访问会长时间停留在序列中。一般而言,DRAM控制器能够进行的工作越多,它处理的SoC体系结构和组合任务就越具体。这就把难题留给了系统设计人员。

Altera SoC 电容 放大器 电压 总线 显示器 收发器 仿真 FPGA ARM 相关文章:

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 真实环境中的系统设计(09-09)

- IoT促进了低功耗的发展(12-05)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)

- 可穿戴电子系统的发展——人类和嵌入式系统的结合(12-05)