SoC:IP是新的抽象

时间:10-24

来源:互联网

点击:

作者:Ron Wilson

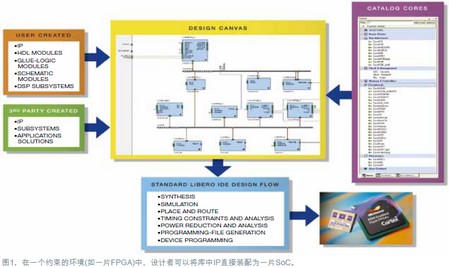

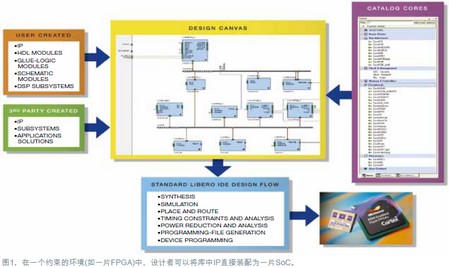

为了应付日益增长的复杂性,必须提高抽象的水平。但当摩尔定律将SoC(系统单芯片)的复杂性加速到逃逸速度时,哪里能找到一种作为RTL(寄存器传输级)补充的新抽象方法?很多观察家注意到,面向硬件的文本式RTL可替代逻辑图,从而推断认为某种系统级描述语言(如SystemC)将提供下一个好的抽象。不过这种情况并不会出现。

Atrenta公司主席、总裁兼首席执行官Ajoy Bose认为:“可重用IP(智能产权)才是新的抽象等级。”如果看看SoC设计团体正在做的工作,就会发现,创建SoC的过程就是对以前所用IP的寻找、特性确定和装配过程。无论是哪种设计创建工具(SystemC、Verilog亦或逻辑图),都只是扮演一个填充空白的角色,如专利功能以及IC的缔结组织结构。但正如大量EDA公司、代工厂和大多数SoC设计者所想象的那样,今天的设计流已经缓慢地认识到了这个现实。看一下自己的工具,你就会知道每个SoC都开始于一组功能需求,以及一张白纸。实际上,要考虑的是一个SoC设计中真正做什么,以及从这些观察数据中可以抽象出什么结论。

新的抽象

Synopsys公司主席兼首席执行官Aart de Geus喜欢乐高玩具,他还喜欢用它们作为硅IP的比拟。他指出,将IP装配起来创建一片SoC,就像把乐高积木块装成玩具一样。IP块是其中的RTL抽象,就好像乐高积木块要比用塑料或木头,去手工制作出一艘船或一只恐龙来得简单。这种模拟可以一直做下去,直到开始无效。

乐高积木(尤其是高价主题包中的精密积木块)也可以体现出以IP为中心的设计流应该是什么样子。最开始是需求,这与传统设计流没有两样。但以IP为中心的设计流很快就会与传统方式分道扬镳。在传统流程中,要将需求划分为更小的模块,仔细地定义接口,直到这些模块足够小,使RTL设计师能用Verilog编写它们。而以IP为中心的流程则几乎相反:你要选择适用的IP块,将它们与需求匹配,就像装配乐高积木一样。你要尝试尽可能用较少的块,留下的空间尽量少。然后用新代码填充这些空白。

设计流程再继续下去,两种方案仍然是各行其道。传统流程经过了功能验证,综合,分析,时钟、电源和测试的精细插入,后端设计以及收敛,这些过程都在不断去除抽象,创建更多的实现细节,直到需求变成为多层的多边形。在每个新的级别上,流程都要停下来,验证该设计是否仍然满足需求。

而以IP为中心的流程再次走了几乎相反的道路。它的要点是将IP装配为一个满足需求的系统,而尽可能少地寻求有关IP细节的新信息。Bose称:“在装配过程中不要陷入调试IP的误区。”

这种情景对很多团队都很理想,富有吸引力。de Geus说:“例如在中国,设计方法研究的就是如何快速地从定义走到IP列表,再到装配。”

但现实情况通常并不是这样。Open-Silicon公司工程副总裁Taher Madraswala说:“至少今天有些功能有很好的定义,理论上你本可以在整个流程中把它们看作黑箱子,但也仅仅是理论上而已。实际上,最终还要在综合与门级优化时打开黑箱子。”为解决这些问题,必须遍历一个理想的设计流,找到希望与现实之间的差距。你必须考虑IP选择、装配、实现和收敛。

IP选择

从需求到一个IP BOM(物料清单)的过程是变化的,而且很不幸要手工完成。如何从A到B取决于系统的性质、IP的可用性、设计团队在重用方面的经验、芯片差异化的营销计划,以及企业策略等等。这个过程不能依赖的一件事是自动化,Synopsys公司的de Geus指出,理论上说,自动化应不存在障碍。

他发现,在RTL时,Design Compiler能从Verilog源中有效地找出该公司DesignWave的相对复杂块。不过,对于较大的IP块,自动化就不稳定了。他说:“用IP时,块都不太通用,要加入更多的人工选择。”

有些情况下,手工IP选择的轻松程度可以接近于自动化工具。例如,很多较小的SoC仍然采用一种简单的、类似于微控制器的架构:一个CPU核心、一个本地缓存,还有一系列外设接口。所有需要的块一般都能从第三方IP库中获得,再补足AMBA(先进微控制器总线架构)接口的管脚,就可以插接到一起了。对于其它情况,IP的选择并不能从需求明显看出。例如,假设一个智能手机SoC有多种授权与加密的要求。你是获取一个大且昂贵的第三方加密引擎许可证,还是选择一个较小的加密数据路径协处理器?另外,你是用MathWorks的MatLab开发自己的块并做综合,还是采用一个较快的(或第二个)CPU核心,并用软件处理需求?

功能的选择并不是过程的结束。功能类似的模块之间可能有很多方面的差异,包括性能、面积、功耗、接口要求、可配置性、对时钟与电源控制的条件、验证覆盖范围以及使用史。IP块的数据表中应有很多这类信息,但有些需要详细询问该块以往的用户,甚至要做少量反向工程。

要从一个可执行的SoC需求文件去推论出一个复杂IP块,这种逻辑问题也许是可以解决的。大多数需求文档仍然采用人类语言,不过并非可执行格式。此外,选择某个IP所需要的多数支持性信息也是零散的,缺乏标准的格式,并且可能是专有的。显然,自动IP选择还需要做大量工作。

现在存在一种非常有趣且大部分尚未披露的可能性。通常人们认为形式验证是相关的验证工具。但据Jasper设计自动化公司营销与业务发展副总裁Oz Levia称,形式上测试某个特性真实性的能力拥有超出传统验证的应用。例如,设计者可以用Jasper公司的ActiveDesign在开发期间研究RTL,有助于掌控RTL代码的创建。从这个想法扩展开去,Levia描述了Jasper与ARM工程师如何合作起来,将针对ARM存储器相关协议的英语规范手工转换为一个可执行的规范,Jasper再将它综合为一组断言。原理上说,一个设计团队可以使用这个过程,从需求创建出一组断言,然后再用形式工具检查一个IP块与需求的符合程度。可编程IP或可配置IP都会带来挑战,但过程中至少会产生一个将IP块装入一个设计的工作说明。

为了应付日益增长的复杂性,必须提高抽象的水平。但当摩尔定律将SoC(系统单芯片)的复杂性加速到逃逸速度时,哪里能找到一种作为RTL(寄存器传输级)补充的新抽象方法?很多观察家注意到,面向硬件的文本式RTL可替代逻辑图,从而推断认为某种系统级描述语言(如SystemC)将提供下一个好的抽象。不过这种情况并不会出现。

Atrenta公司主席、总裁兼首席执行官Ajoy Bose认为:“可重用IP(智能产权)才是新的抽象等级。”如果看看SoC设计团体正在做的工作,就会发现,创建SoC的过程就是对以前所用IP的寻找、特性确定和装配过程。无论是哪种设计创建工具(SystemC、Verilog亦或逻辑图),都只是扮演一个填充空白的角色,如专利功能以及IC的缔结组织结构。但正如大量EDA公司、代工厂和大多数SoC设计者所想象的那样,今天的设计流已经缓慢地认识到了这个现实。看一下自己的工具,你就会知道每个SoC都开始于一组功能需求,以及一张白纸。实际上,要考虑的是一个SoC设计中真正做什么,以及从这些观察数据中可以抽象出什么结论。

新的抽象

Synopsys公司主席兼首席执行官Aart de Geus喜欢乐高玩具,他还喜欢用它们作为硅IP的比拟。他指出,将IP装配起来创建一片SoC,就像把乐高积木块装成玩具一样。IP块是其中的RTL抽象,就好像乐高积木块要比用塑料或木头,去手工制作出一艘船或一只恐龙来得简单。这种模拟可以一直做下去,直到开始无效。

乐高积木(尤其是高价主题包中的精密积木块)也可以体现出以IP为中心的设计流应该是什么样子。最开始是需求,这与传统设计流没有两样。但以IP为中心的设计流很快就会与传统方式分道扬镳。在传统流程中,要将需求划分为更小的模块,仔细地定义接口,直到这些模块足够小,使RTL设计师能用Verilog编写它们。而以IP为中心的流程则几乎相反:你要选择适用的IP块,将它们与需求匹配,就像装配乐高积木一样。你要尝试尽可能用较少的块,留下的空间尽量少。然后用新代码填充这些空白。

设计流程再继续下去,两种方案仍然是各行其道。传统流程经过了功能验证,综合,分析,时钟、电源和测试的精细插入,后端设计以及收敛,这些过程都在不断去除抽象,创建更多的实现细节,直到需求变成为多层的多边形。在每个新的级别上,流程都要停下来,验证该设计是否仍然满足需求。

而以IP为中心的流程再次走了几乎相反的道路。它的要点是将IP装配为一个满足需求的系统,而尽可能少地寻求有关IP细节的新信息。Bose称:“在装配过程中不要陷入调试IP的误区。”

这种情景对很多团队都很理想,富有吸引力。de Geus说:“例如在中国,设计方法研究的就是如何快速地从定义走到IP列表,再到装配。”

但现实情况通常并不是这样。Open-Silicon公司工程副总裁Taher Madraswala说:“至少今天有些功能有很好的定义,理论上你本可以在整个流程中把它们看作黑箱子,但也仅仅是理论上而已。实际上,最终还要在综合与门级优化时打开黑箱子。”为解决这些问题,必须遍历一个理想的设计流,找到希望与现实之间的差距。你必须考虑IP选择、装配、实现和收敛。

IP选择

从需求到一个IP BOM(物料清单)的过程是变化的,而且很不幸要手工完成。如何从A到B取决于系统的性质、IP的可用性、设计团队在重用方面的经验、芯片差异化的营销计划,以及企业策略等等。这个过程不能依赖的一件事是自动化,Synopsys公司的de Geus指出,理论上说,自动化应不存在障碍。

他发现,在RTL时,Design Compiler能从Verilog源中有效地找出该公司DesignWave的相对复杂块。不过,对于较大的IP块,自动化就不稳定了。他说:“用IP时,块都不太通用,要加入更多的人工选择。”

有些情况下,手工IP选择的轻松程度可以接近于自动化工具。例如,很多较小的SoC仍然采用一种简单的、类似于微控制器的架构:一个CPU核心、一个本地缓存,还有一系列外设接口。所有需要的块一般都能从第三方IP库中获得,再补足AMBA(先进微控制器总线架构)接口的管脚,就可以插接到一起了。对于其它情况,IP的选择并不能从需求明显看出。例如,假设一个智能手机SoC有多种授权与加密的要求。你是获取一个大且昂贵的第三方加密引擎许可证,还是选择一个较小的加密数据路径协处理器?另外,你是用MathWorks的MatLab开发自己的块并做综合,还是采用一个较快的(或第二个)CPU核心,并用软件处理需求?

功能的选择并不是过程的结束。功能类似的模块之间可能有很多方面的差异,包括性能、面积、功耗、接口要求、可配置性、对时钟与电源控制的条件、验证覆盖范围以及使用史。IP块的数据表中应有很多这类信息,但有些需要详细询问该块以往的用户,甚至要做少量反向工程。

要从一个可执行的SoC需求文件去推论出一个复杂IP块,这种逻辑问题也许是可以解决的。大多数需求文档仍然采用人类语言,不过并非可执行格式。此外,选择某个IP所需要的多数支持性信息也是零散的,缺乏标准的格式,并且可能是专有的。显然,自动IP选择还需要做大量工作。

现在存在一种非常有趣且大部分尚未披露的可能性。通常人们认为形式验证是相关的验证工具。但据Jasper设计自动化公司营销与业务发展副总裁Oz Levia称,形式上测试某个特性真实性的能力拥有超出传统验证的应用。例如,设计者可以用Jasper公司的ActiveDesign在开发期间研究RTL,有助于掌控RTL代码的创建。从这个想法扩展开去,Levia描述了Jasper与ARM工程师如何合作起来,将针对ARM存储器相关协议的英语规范手工转换为一个可执行的规范,Jasper再将它综合为一组断言。原理上说,一个设计团队可以使用这个过程,从需求创建出一组断言,然后再用形式工具检查一个IP块与需求的符合程度。可编程IP或可配置IP都会带来挑战,但过程中至少会产生一个将IP块装入一个设计的工作说明。

SoC Verilog EDA 自动化 总线 ARM 仿真 快速原型 FPGA 意法半导体 恩智浦 飞思卡尔 半导体 电源管理 电流 电路 相关文章:

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)