SoC:IP是新的抽象

时间:10-24

来源:互联网

点击:

装配

IP装配是以IP为中心设计的流程基础。有些设计者使用“装配”,而不是“集成”,以示一种重要的区别。在这个阶段的想法是,将IP块看作是可配置的黑箱,而只编写一些在完成黑箱配置后,要将它们胶合到一起的RTL。这种情况与“集成”这一名词所代表的日益膨胀IP块有很大不同。

理想的装配过程必须开始于系统级仿真。在另一个意义上,系统仿真就是IP选择的验证阶段:你要检验所选择的IP块是否能以一种满足系统需求的方式联结在一起。de Geus说:“在一个IP装配流中,系统校验与验证更加重要。通常,我们需要一个快速的原型来验证软件可以在芯片上工作。”

快速原型的重要性表明,IP块的事务级模型可能很有价值。但IP供应商有时并没有事务级模型,或这些模型对现有IP版本不再正确。不过,你几乎总能用到软IP的RTL源,从而创建基于FPGA的快速原型,这就是FPGA原型对IP中心化设计的重要性。

另外,还可以在装配期间做另一种早期评估。静态分析可以检查IP有无违背规则,是否符合最佳实践。评估通常可以相当接近于最终芯片的功耗、性能和面积。Atrenta公司的Bose说:“今天,使用高等级综合的结果要比用软IP有更多的不确定性。”

在一个理想化的世界里,一旦将各个块装入原型,验证了系统的性能,并研究了大致的特性,则要做的唯一验证工作将是现有块和新块之间的连接情况。但不同的情况下,对于理想的接近程度也会不同。

也许最接近于理想的方案是:IP、互连,以及IC实现全是一个来源(图1)。附文“FPGA的情况”是这种情况的一个实例。真实世界里确实能有这种好运气,但仅适用于那些有强大的设计重用文化的垂直型集成公司,如IBM、意法半导体、几家最大的日本公司,以及在私募投资者重新关注自己优先权以前的恩智浦和飞思卡尔。如果没有强大的企业重用文化,以及公司对IP开发过程的控制,很难获得一种纯粹的黑箱装配流程。Bose说:“人们仍然懒于做实现重用所需的少量额外工作。”他表示日本的STARC(半导体技术学术研究中心)提供了一本出色的重用手册。不过,有些开发IP的团队缺乏训练与管理支持,不能在这个等级上使自己的设计可重用化。

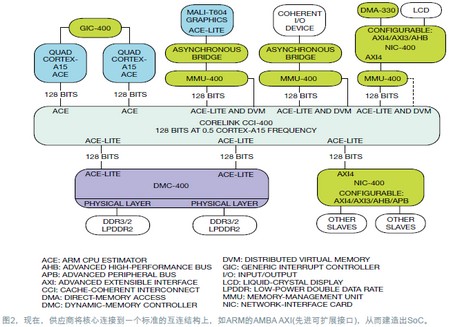

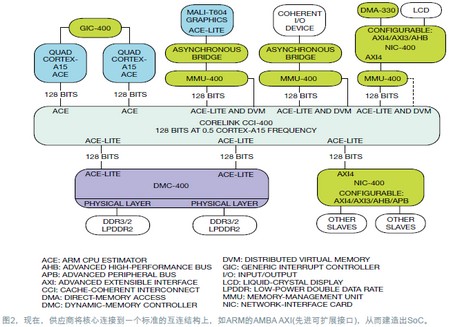

下一个最接近理想环境的就是工业标准(如AMBA),它定义了块间的全部互连,还有所有符合标准的IP(图2)。此时,装配只是要确保信号名称以及极性一致,并且所有接口都可以工作在所要求频率上。如果没有一个统一的总线标准,则事情就变得更复杂了。你必须根据已配置IP块的实例去了解接口,必要情况下,还要创建额外的RTL胶合逻辑,以执行各块之间的事务,并且必须验证所有这些工作。

Open-Silicon的Madraswala称,关键是寻找到一种验证交互作用的方式,而不用验证IP的所有内部东西。他说:“你可以利用IP以前已被用过这一事实。看看自己的计划日期表,决定把自己的验证时间花在什么地方。你可能更愿意编写断言或测试,来验证IP数据表中的逻辑集成要求,而不是做一个全面的验证计划。但要知道检查什么和不检查什么,经验很关键。”Madraswala补充说,这种验证方案对仿真的依赖高于形式工具。

实现

在这一点上,IP中心设计流开始与传统流程重新汇合了。软IP块、新的块以及互连都要去做综合,并进入扫描插入、布局与布线。硬IP也进入了布局布线的流程。然后,团队关闭设计。不过,在某些方面,IP为中心的设计仍有自己的独特性。

Madraswala认为,差异之一是电源管理的方案。他说:“针对电源管理的设计调整正在成为设计流的一个独立阶段。这正在成为一种独有的艺术与技术。”Madraswala解释说,当你自己设计一个块时,可以使用综合开关,做再对位以简化时序;做精细粒度的时钟门控,以及其它网表级的优化技术,其中大部分可获得功耗的优势。

举例来说,其它工具可以改变时钟的偏移,以控制峰值的时钟电流。Teklatech公司首席执行官Tobias Bjerregaard说,用综合开关也可以做一些此类工作,但工程师们仍然会手工完成这些任务。所有这些技术都非常有用,但全都用于第三方IP也许并不明智。

Madraswala称:“我们可能没有原始源码,因此无法做等效性检查。通常我们没有权利去改变块的设计。”问题是,对一个许可证优化到何种地步,才会违反一个IP块的保证条款,这件事很难确定。

Synopsys公司的de Geus也怀疑对等效性检查器的依赖性,但原因不同。他说:“形式工具不断地寻找可以生成的综合。例如,综合工具可以做延迟浏览,但形式等效性检查器却可能看不到与原电路等效的重组电路。 ”

相反,Open-Silicon的Madraswala则建议在块级对IP使用时钟门控与电源门控。他解释说:“我们围绕代码放了一个封装器,让它表现出我们想要的方式。”这种方案避免了修改第三方的代码。Madraswala说,物理设计仍保持传统方式。硬IP块加入了布局布线流程,具体要依赖于供应商的集成指导。Madraswala说,他的公司会对块运行一个DRC(设计规则检查),以确保它符合当前的规则平台,并与供应商对集成进行目视评估。他说:“有时候,他们尚未写好有些指南。”Open-Silicon在这个过程后会做一个平面设计的DRC,但Madraswala称,99%的情况下不会有任何问题。

相对来说,后端流程从基于IP的设计获益不多。除FPGA设计以外,都不能省略DRC、提取或时序、信号完整性,以及功率完整性的收敛。在这些领域中,仍留有太多的技巧和细节,如不同的约束、电源管理策略以及DFT(可测试设计)方案。这些差异可能只在集成后的芯片上才体现出来。不过,仍然存在着以IP为中心设计流的理想情况,这就是选择并嵌合起多个块、验证互连,然后按一个键就获得了最终设计。

这样一个流程要求非常训练有素的IP设计人员。de Geus认为:“乐高积木的智力只限于思考插头与插座,但这只走了一半。另一半是弄明白如何保持非常严格的公差,使插头与插座可以反复再三地工作,而不会卡住或松脱。”这也适用于以IP为中心流程的进一步自动化:能与门控起到同等作用的也许就是提高IP的标准化水平和创建技巧。

IP装配是以IP为中心设计的流程基础。有些设计者使用“装配”,而不是“集成”,以示一种重要的区别。在这个阶段的想法是,将IP块看作是可配置的黑箱,而只编写一些在完成黑箱配置后,要将它们胶合到一起的RTL。这种情况与“集成”这一名词所代表的日益膨胀IP块有很大不同。

理想的装配过程必须开始于系统级仿真。在另一个意义上,系统仿真就是IP选择的验证阶段:你要检验所选择的IP块是否能以一种满足系统需求的方式联结在一起。de Geus说:“在一个IP装配流中,系统校验与验证更加重要。通常,我们需要一个快速的原型来验证软件可以在芯片上工作。”

快速原型的重要性表明,IP块的事务级模型可能很有价值。但IP供应商有时并没有事务级模型,或这些模型对现有IP版本不再正确。不过,你几乎总能用到软IP的RTL源,从而创建基于FPGA的快速原型,这就是FPGA原型对IP中心化设计的重要性。

另外,还可以在装配期间做另一种早期评估。静态分析可以检查IP有无违背规则,是否符合最佳实践。评估通常可以相当接近于最终芯片的功耗、性能和面积。Atrenta公司的Bose说:“今天,使用高等级综合的结果要比用软IP有更多的不确定性。”

在一个理想化的世界里,一旦将各个块装入原型,验证了系统的性能,并研究了大致的特性,则要做的唯一验证工作将是现有块和新块之间的连接情况。但不同的情况下,对于理想的接近程度也会不同。

也许最接近于理想的方案是:IP、互连,以及IC实现全是一个来源(图1)。附文“FPGA的情况”是这种情况的一个实例。真实世界里确实能有这种好运气,但仅适用于那些有强大的设计重用文化的垂直型集成公司,如IBM、意法半导体、几家最大的日本公司,以及在私募投资者重新关注自己优先权以前的恩智浦和飞思卡尔。如果没有强大的企业重用文化,以及公司对IP开发过程的控制,很难获得一种纯粹的黑箱装配流程。Bose说:“人们仍然懒于做实现重用所需的少量额外工作。”他表示日本的STARC(半导体技术学术研究中心)提供了一本出色的重用手册。不过,有些开发IP的团队缺乏训练与管理支持,不能在这个等级上使自己的设计可重用化。

下一个最接近理想环境的就是工业标准(如AMBA),它定义了块间的全部互连,还有所有符合标准的IP(图2)。此时,装配只是要确保信号名称以及极性一致,并且所有接口都可以工作在所要求频率上。如果没有一个统一的总线标准,则事情就变得更复杂了。你必须根据已配置IP块的实例去了解接口,必要情况下,还要创建额外的RTL胶合逻辑,以执行各块之间的事务,并且必须验证所有这些工作。

Open-Silicon的Madraswala称,关键是寻找到一种验证交互作用的方式,而不用验证IP的所有内部东西。他说:“你可以利用IP以前已被用过这一事实。看看自己的计划日期表,决定把自己的验证时间花在什么地方。你可能更愿意编写断言或测试,来验证IP数据表中的逻辑集成要求,而不是做一个全面的验证计划。但要知道检查什么和不检查什么,经验很关键。”Madraswala补充说,这种验证方案对仿真的依赖高于形式工具。

实现

在这一点上,IP中心设计流开始与传统流程重新汇合了。软IP块、新的块以及互连都要去做综合,并进入扫描插入、布局与布线。硬IP也进入了布局布线的流程。然后,团队关闭设计。不过,在某些方面,IP为中心的设计仍有自己的独特性。

Madraswala认为,差异之一是电源管理的方案。他说:“针对电源管理的设计调整正在成为设计流的一个独立阶段。这正在成为一种独有的艺术与技术。”Madraswala解释说,当你自己设计一个块时,可以使用综合开关,做再对位以简化时序;做精细粒度的时钟门控,以及其它网表级的优化技术,其中大部分可获得功耗的优势。

举例来说,其它工具可以改变时钟的偏移,以控制峰值的时钟电流。Teklatech公司首席执行官Tobias Bjerregaard说,用综合开关也可以做一些此类工作,但工程师们仍然会手工完成这些任务。所有这些技术都非常有用,但全都用于第三方IP也许并不明智。

Madraswala称:“我们可能没有原始源码,因此无法做等效性检查。通常我们没有权利去改变块的设计。”问题是,对一个许可证优化到何种地步,才会违反一个IP块的保证条款,这件事很难确定。

Synopsys公司的de Geus也怀疑对等效性检查器的依赖性,但原因不同。他说:“形式工具不断地寻找可以生成的综合。例如,综合工具可以做延迟浏览,但形式等效性检查器却可能看不到与原电路等效的重组电路。 ”

相反,Open-Silicon的Madraswala则建议在块级对IP使用时钟门控与电源门控。他解释说:“我们围绕代码放了一个封装器,让它表现出我们想要的方式。”这种方案避免了修改第三方的代码。Madraswala说,物理设计仍保持传统方式。硬IP块加入了布局布线流程,具体要依赖于供应商的集成指导。Madraswala说,他的公司会对块运行一个DRC(设计规则检查),以确保它符合当前的规则平台,并与供应商对集成进行目视评估。他说:“有时候,他们尚未写好有些指南。”Open-Silicon在这个过程后会做一个平面设计的DRC,但Madraswala称,99%的情况下不会有任何问题。

相对来说,后端流程从基于IP的设计获益不多。除FPGA设计以外,都不能省略DRC、提取或时序、信号完整性,以及功率完整性的收敛。在这些领域中,仍留有太多的技巧和细节,如不同的约束、电源管理策略以及DFT(可测试设计)方案。这些差异可能只在集成后的芯片上才体现出来。不过,仍然存在着以IP为中心设计流的理想情况,这就是选择并嵌合起多个块、验证互连,然后按一个键就获得了最终设计。

这样一个流程要求非常训练有素的IP设计人员。de Geus认为:“乐高积木的智力只限于思考插头与插座,但这只走了一半。另一半是弄明白如何保持非常严格的公差,使插头与插座可以反复再三地工作,而不会卡住或松脱。”这也适用于以IP为中心流程的进一步自动化:能与门控起到同等作用的也许就是提高IP的标准化水平和创建技巧。

SoC Verilog EDA 自动化 总线 ARM 仿真 快速原型 FPGA 意法半导体 恩智浦 飞思卡尔 半导体 电源管理 电流 电路 相关文章:

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)