FPGA学习资料汇总,免费下载

有问题都能找到。本视频就告诉你,即使是测试文件问题,你也能通过我们的方法,顺藤摸瓜,把问题找到。

04 定位问题案例3

我们是否曾经遇到这样的情况:已经找到具体的某一行代码有问题,通过波形和代码一一对照,波形就是与代码不一致,这个时候甚至你都怀疑仿真软件是否出现了BUG。

但是,首先相信一点,仿真软件出BUG的可能性微乎其微,本视频就通过一个具体的案例,教你如何定位这种错误。

相信一个真理,FPGA是很简单的,是0就是0,是1就是1,不会有奇怪的现象的。当你发现很奇怪的时候,一般就是自己粗心了。

05 定位问题案例4

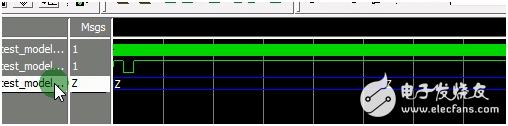

仿真出现高阻态(下图),是不是很常见?你是怎么定位的呢?是不是急急忙忙去求助?本视频告诉你,别急,高阻态也能用我们方法定位。

06 定位问题案例5

又一个常见的错误类似,输出的值也是高阻类,再次看看用明德扬方法是如何定位的,提高一下能力,以后再遇到问题就不慌了。

07 定位问题案例6

我明明在测试文件产生了时钟,但仿真时却发现时钟信号一直为0。你的第一反应是不是去检查代码?别忘了,我们一直强调的定位思维。任何错误都不要去检查代码来发现,而是要通过定位的思维。前者找到问题靠运气,后者找到问题那是一定的。

本视频用一个案例告诉你,通过我们方法去定位到某一行,认定就是这一行出错,盯着去思考,就能发现问题。

3.明德扬GVIM设计模板

01 基于明德扬课程的GVIM教程

本视频介绍基于明德扬课程的GVIM模板。明德扬鼓励大家多用模板,优点具体如下:

1. 多用模板有利于我们专注设计。FPGA学习的核心是“设计”,使用模板,能够让学员专心于设计,不用耗费大量时间在无用的地方。

2. 多用模板有利于我们规范设计。FPGA设计规范非常重要,明德扬要求学员按模板的要求进行设计,从而得到最优化、最规范的代码。

3. 多用模板有利于我们节省时间。明德扬的模板,包含了至简设计法的计数器、状态机、FIFO和模块结构等,这些是RTL代码最常见的部分。使用这些模板的时候,工程师只需按顺序填空,就能快速地进行设计,可节省大量时间。

本视频介绍了明德扬精心制作的常用模板,快来看看我们模板的神奇效果吧!

02 利用GVIM制作模板

上一节我们介绍了明德扬的常用模板,你是不是也心动了,想制作自己的个性化模板?本视频将介绍在GVIM当中如何制作自己的模板!

4.明德扬时序约束视频简介

FPGA时序约束是FPGA设计中的一个重点,也是难点。很多人面对各种时序概念、时序计算公式、时序场景是一头乱麻,望而生畏。

现有的教材大部分是介绍概念、时序分析工具和计算公式的。我们学习教材之后觉得已经完全掌握,但是当需要真正做项目的时候,就会有无从下手的感觉。例如,那些计算时序的公式,真的要一五一十地套下去,估计自己心里也没底吧。

明德扬最看重的是实践,一切不能用于实践的理论都是扯淡。为此,明德扬抛开一切复杂的理论,就从工程实践的角度来讲解时序约束。

我们的做法:先把时序约束分成几个类别,其中每个类别又分成几个场景,将每个场景下所对应的时序约束方法一一列出后,提供每个时序约束参数的获取方法,最后填好数值,完毕。

我们的目标:第一,按我们提供的步骤一个一个进行约束;第二,根据自己的使用情况,找到对应的场景后,挑出其所对应的时序约束;第三,根据提示的方法,得到参数,计算出最终结果。

我们的优势:一个傻瓜式、但实用的时序约束“操作手册”。

本系列视频,简单介绍了我们的“操作手册”,保证让你有意外的收获!

另外,FPGA是实践课程,听一千遍,不如自己动手实践,练习才是最重要的内容。欢迎关注我们获取更多资料。

01 时序约束步骤

本视频讲述时序约束步骤:约束有很多,并且总是有先后的,先约束哪些,再约束哪些,都有讲究。按工程需要,定义好步骤,这样就能一步一步约束,逐个思考,最终完成。

02 生成时钟约束

时钟约束是工程一开始就进行的约束。时钟约束又可以分成三大类:输入时钟、PLL等衍生时钟和自己分步时钟。每一种都有自己的约束方法,详情请看视频介绍。

03 input delay约束

输入延时约束是约束的重点。明德扬把输入约束分成三大类:系统同步、源同步和无时钟数据,其中源同步分成SDR和DDR两场景,而DDR又可再细分成边沿对齐和中心对齐。

以上每种情况,其约束语句、获取参数的方法都是不一样的。

想知道具体情况,欢迎观看本节视频。

04 output delay约束

输出延时约束和输入延时一样,也是约束的重点。按照同样的思路,明德扬把输出约束分

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)