例说FPGA连载31:PLL例化配置与LED之PLL的IP核配置

时间:09-12

来源:互联网

点击:

C1的时钟频率为33.3333MHz,相位为0deg,占空比为50%。

● C2的时钟频率为50MHz,相位为0deg,占空比为50%。

● C3的时钟频率为65MHz,相位为0deg,占空比为50%。

● C4的时钟频率为100MHz,相位为0deg,占空比为50%。

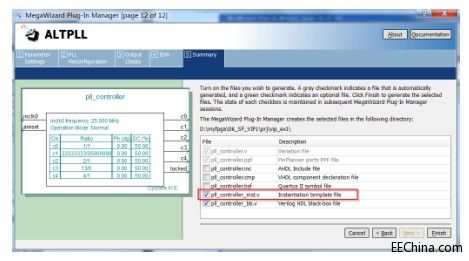

配置完成后,最后在Summary页面,如图3.16所示,勾选上*_inst.v文件,这是一个PLL例化的模板文件,一会我们可以在工程目录下找到这个文件,然后打开它,将它的代码复制到工程中,修改对应接口即可完成这个IP核的集成。

图3.16 Summary配置页面

点击Finish完成PLL的配置。工程中若弹出如图3.17所示的对话框,勾选“Automatically add Quartus II IP Files to all projects”选项后,点击Yes。

图3.17 自动添加文件窗口

FPGA LED 振荡器 电子 Verilog Quartus 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)