例说FPGA连载31:PLL例化配置与LED之PLL的IP核配置

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

本实例使用了一个PLL的硬核IP模块。关于PLL,这里简单的做些基础扫盲。

PLL(Phase Locked Loop),即锁相回路或锁相环。PLL用于振荡器中的反馈技术。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

时钟就是FPGA运行的心脏,它的每次跳动必须精准而毫无偏差(当然现实世界中不存在所谓的毫无偏差,但是我们希望它的偏差越小越好)。一个FPGA工程中,不同的外设通常工作在不同的时钟频率,所以一个时钟肯定满足不了需求;此外,有时候可能两个不同的模块共用一个时钟频率,但是由于他们运行在不同的工作环境和时序下,所以他们常常是同频不同相(相位),怎么办?用PLL呗。当然了,我们的FPGA里面定义的PLL,可不是仅仅只有一个反馈调整功能,它还有倍频和分频等功能集成其中。严格一点讲,我觉得这个PLL实际上应该算是一个FPGA内部的时钟管理模块了。不多说,如图3.9所示,大家看看PLL内部的功能框图自己体味体味。

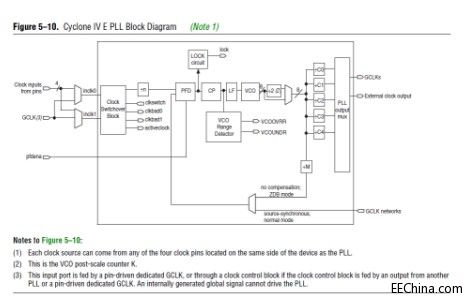

图3.9 PLL内部功能结构

详细的工作机理请大家参考Cyclone IV Device Handbook, Volume1的Chapter 5的内容。

Cyclone IV的PLL输入一个时钟信号,最多可以产生5个输出时钟信号,输出的频率和相位都可以在一定的范围内调整。

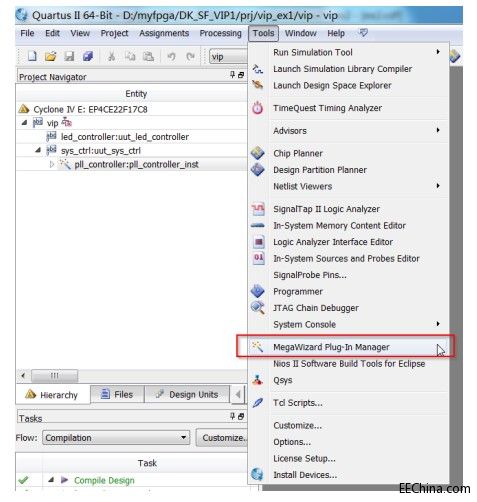

下面我们来看本实例如何配置一个PLL硬核IP,并将其集成到工程中。如图3.10所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Manager”。

图3.10 菜单选择MegaWizard

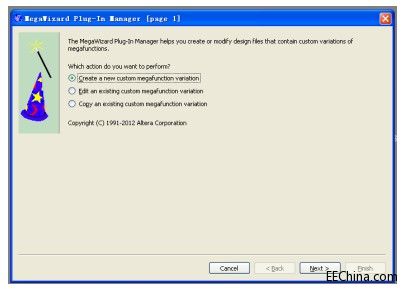

如图3.11所示,选择“Creat a new custom megafunction variation”,然后Next。

图3.11 新建MegaWizard

接着选择我们所需要的IP核,如图3.12所示进行设置。

● 在“Select a megafunction from the list below”下面选择IP核为“I/O à ALTPLL”。

● 在“What device family will you be using”后面的下拉栏中选择我们所使用的器件系列为“Cyclone IV E”。

● 在“What type of output file do you want to create?”下面选择语言为“Verilog”。

● 在“What name do you want for the output file?”下面输入工程所在的路径,并且在最后面加上一个名称,这个名称是我们现在正在例化的PLL模块的名称,我们可以给他起名叫pll_controller,然后点击Next进入下一个页面。

图3.12 选择ALTPLL IP核

接着来到了PLL的参数配置页面,做如图3.13所示的设置。然后点击Next进入下一个页面。

● 在“What device speed grade will you be using?”后面选择“8”,即我们使用的器件的速度等级。

● 在“What is the frequency of the inclk0 input?”后面选择“25MHz”,即我们输入到该PLL的基准时钟频率。

图3.13 PLL参数设置

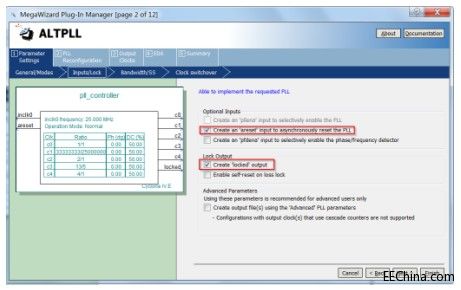

Input/lock页面中,如图3.14所示进行设置,接着点击Next进入下一个页面。

● 勾选“Create an ‘areset’ input to asynchronously reset the PLL”,即引出该PLL硬核的’areset’信号,这是该PLL硬核的异步复位信号,高电平有效。

● 勾选“Create ‘locked’ output”,即引出该PLL硬核的’locked’信号,该信号用于指示PLL是否完成内部初始化,已经可以正常输出了高电平有效。

图3.14 PLL复位和锁定信号设置

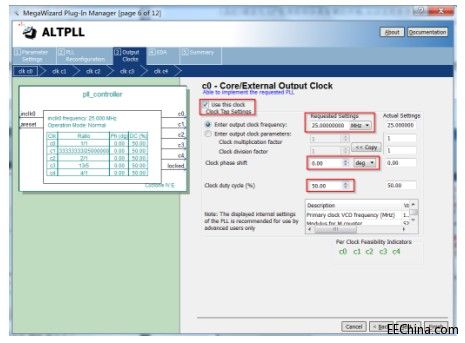

Bandwidth/SS、Clock Switchover和PLL Reconfiguration页面不用设置,默认即可。直接进入Ouput Clocks页面,如图3.15所示,这里有5个可选的时钟输出通道,通过勾选对应通道下方的Use this clock选项开启对应的时钟输出通道。可以在配置页面中设置输出时钟的频率、相位和占空比。这里是 C0通道的设置。

● 勾选“Use this clock”,表示使用该时钟输出信号。

● 输入“Enter output clock frequency”为“25MHz”,表示该通道输出的时钟频率为25MHz。

● 输入“Clock phase shift”为“0 deg”,表示该通道输出的时钟相位为0 deg。

● 输入“Clock duty cycle(%)”为“50.00%”,表示该通道输出的时钟占空比为50%。

图3.15 PLL输出时钟C0设置

和C0的配置一样,我们可以分别开启并且配置C1、C2、C3和C4,这些时钟虽然这个例程暂时用不上,但是后续的例程将会使用到。

●

FPGA LED 振荡器 电子 Verilog Quartus 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)