例说FPGA连载18:配置电路设计

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

我们所说的FPGA配置电路,一方面要完成从PC上把bit文件下载到FPGA或存储器的任务,另一方面则要完成FPGA上电启动时加载配置数据的任务。在开始设计FPGA的配置电路之前,我们不妨花一些篇幅简单的了解一下FPGA的配置过程和配置方式。

大都数FPGA器件都是基于RAM结构的,当然了,也有基于Flash结构的,但RAM结构的是主流,也是我们讨论的重点。而RAM是易失存储器,在掉电后保存在上面的数据就丢失了,重新上电后需要再次加载配置数据。因此,我们肯定不希望每次重新上电后都用PC去加载一次,工程应用也不允许我们这么做。所以,FPGA旁边都有一颗配置芯片,它通常是一颗Flash存储器。不管是串行还是并行的Flash,它们的启动加载原理基本相同。

为避免混淆,这里对FPGA的下载配置和启动配置做一点区分。FPGA器件的下载配置,是指将PC上的FPGA配置数据流通过下载线缆烧录到FPGA或者Flash存储器中。而FPGA器件的启动配置,则是指将配置数据流从PC或者Flash存储器中加载到FPGA内,使其运行起来。

FPGA器件的下载配置,最常见的是基于JTAG的配置方式,这种方式既可以直接将PC上的配置数据流加载到FPGA上在线运行,也可以通过FPGA器件本身间接的将数据烧录到Flash等外部配置芯片中。另一种下载配置是将配置数据流直接下载到配置芯片中。由于JTAG方式灵活多用,尤其是在线调试非常快速便利,因此我们的FPGA核心板电路中就只预留了JTAG接口。

FPGA器件的启动配置主要有JTAG方式,AS和PS配置方式。

AS配置方式由FPGA器件引导配置过程,它控制着外部存储器及其初始化过程。FPGA器件处于主动地位,配置器件处于从属地位。配置数据通过DATA0引脚送入 FPGA。配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS配置方式则由PC或其它控制器控制配置过程。在PS配置期间,配置数据从外部储存器件通过DATA0引脚送入FPGA。配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在RAM中,加电时须重新下载。在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS配置方式。在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中FPGA配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

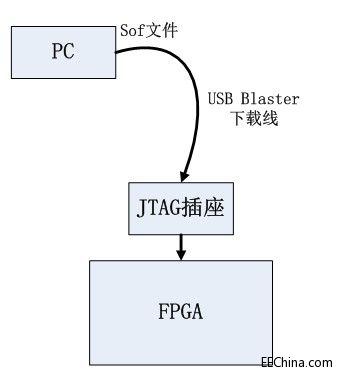

JTAG模式在线下载FPGA的原理如图2.21所示,PC端的Quartus II软件通过下载线缆将配置数据流(sof文件)下载到FPGA内部,下载完成后FPGA中立刻执行下载代码,速度很快,非常适合调试。

图2.21 JTAG方式下载配置过程

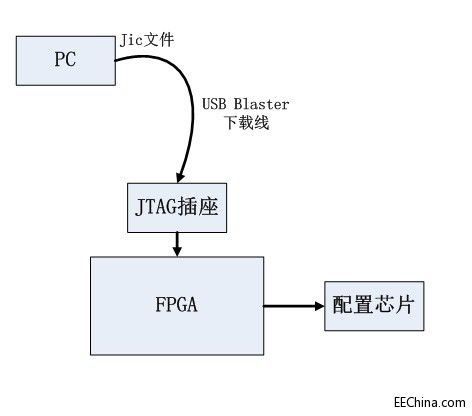

FPGA下载数据到配置芯片的原理如图2.22所示,PC端的Quartus II软件通过下载线缆将配置数据流(jic文件)下载到配置芯片中。由于配置芯片和JTAG接口都是分别连接到FPGA的,他们不是直接连接,所以配置文件从PC先是传送到FPGA,然后FPGA内部再转送给配置芯片,这个过程FPGA相当于起到一个桥接的作用。

图2.22 JTAG方式下载数据到配置芯片

看完JTAG模式下在线配置FPGA和烧录配置芯片的原理,我们再了解一下FPGA上电初始的配置过程。FPGA上电后,内部的控制器首先工作,确认当前的配置模式,如果是外部配置芯片启动,则通过和外部配置芯片的接口(如我们的SPI接口)将配置芯片的数据加载到FPGA的RAM中,配置完成后开始正式运行。当然了,有人可能在想,JTAG在线配置是否和配置芯片加载相冲突呢?非也,JTAG在线配置的优先级是最高的,无论此时FPGA中在运行什么逻辑,只要JTAG下载启动,则FPGA便停下当前的工作,开始运行JTAG下载的新的配置数据。

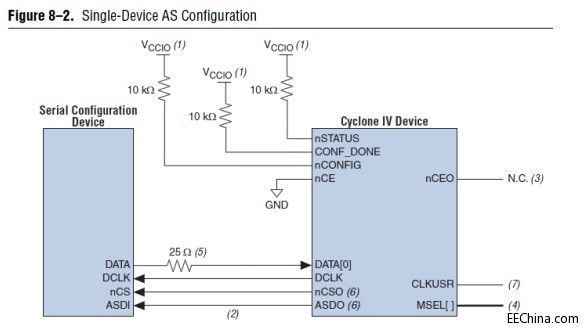

先看器件手册中给出的一些相关参考设计,如图2.23所示,这是FPGA和用于配置的SPI Flash的接口连接方式,即我们所说的AS配置方式。注意FPGA的几个主要引脚nSTATUS\CONF_DONE\nCONFIG\nCE的连接,或者上拉,或者接地,主要是为了保证这些信号在上电初始处于一个确定的电平状态,防止错误电平导致误触发。DATA\DCLK\NCSO\ASDO这4个引脚便是SPI接口,连接到SPI Flash。

图2.23 AS配置参考电路的截图

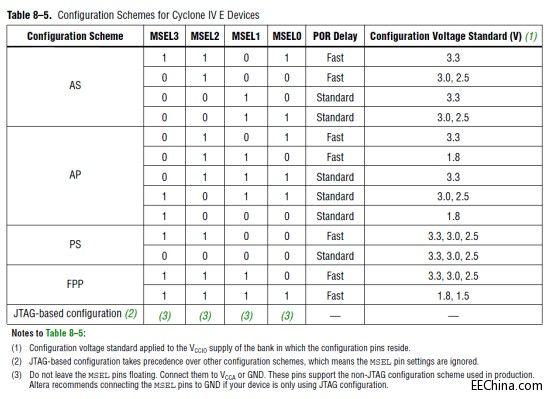

如图2.24所示,FPGA有组MSEL引脚是用于设置FPGA初上电时的启动模式,我们的FPGA上电使用Standard AS模式从SPI Flash里面加载配置数据。

图2.24 MSEL引脚配置说

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)