例说FPGA连载26:AV视频采集子板设计

时间:08-31

来源:互联网

点击:

例说FPGA连载26:AV视频采集子板设计

特权同学,版权所有

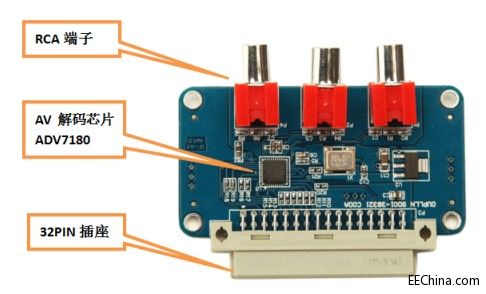

SF-AV子板的实物照片如图2.45所示。

图2.45 SF-AV子板实物照片

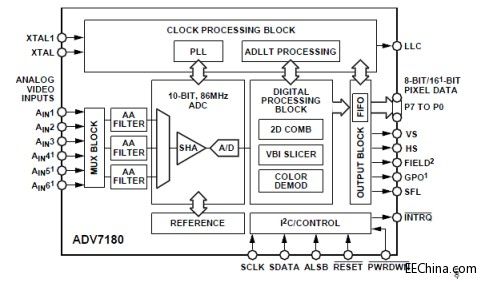

SF-AV子板板载的ADV7180芯片是一颗AV解码芯片,该芯片能够自动检测并转换标准的AV电视信号,包括NTSC、PAL和SECAM等制式。该芯片输出的数字信号接口为标准的ITU-R BT.656协议。

图2.46 ADV7180芯片内部功能框图

SF-AV子板的主要接口定义如表2.7所示。

表2.7 SF-AV子板连接引脚定义

名称 | 位置 | 功能描述 |

SDA | P3-5 | IIC配置数据信号。 |

SCL | P3-8 | IIC配置时钟信号。 |

RESET_N | P3-6 | 复位信号,低电平有效。 |

VSY | P3-7 | ITU-R BT.656接口场同步信号。 |

HSY | P3-10 | ITU-R BT.656接口行同步信号。 |

LLC | P3-28 | ITU-R BT.656接口时钟信号。 |

D0 | P3-19 | ITU-R BT.656接口数据总线。 |

D1 | P3-17 | ITU-R BT.656接口数据总线。 |

D2 | P3-16 | ITU-R BT.656接口数据总线。 |

D3 | P3-13 | ITU-R BT.656接口数据总线。 |

D4 | P3-14 | ITU-R BT.656接口数据总线。 |

D5 | P3-11 | ITU-R BT.656接口数据总线。 |

D6 | P3-12 | ITU-R BT.656接口数据总线。 |

D7 | P3-9 | ITU-R BT.656接口数据总线。 |

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)