无中断更新I/O:克服高可用性系统的设计挑战

时间:06-23

来源:互联网

点击:

作者:莱迪思半导体,Shyam Chandra

高可用性系统,如服务器、通信网关和基站等需要持续工作。一旦现场安装后,就需要通过软件升级来增强系统功能和修复错误。因此,这些系统设计需可以在不中断其正常运行的情况下进行系统功能更新。可编程逻辑器件(PLD)常被用于支持在系统设计更新。使用PLD的改进后的设计成本更低、使用更方便、性能更强,使得可编程逻辑器件成为这些系统中理想的板上硬件管理器件,可管理板上DC-DC转换器、监测和控制关键信号、集合串口通信并执行其他内务管理功能。

不可或缺的PLD

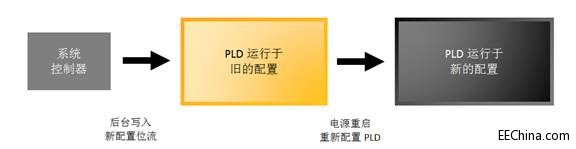

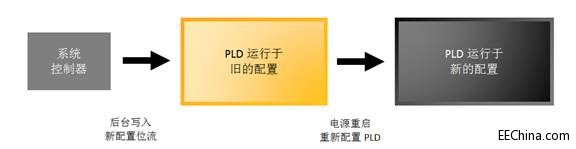

PLD包含一系列可编程功能单元。这些单元的配置和互连实现了板上特定的硬件管理功能。通常情况下,一个软件设计工具将某个逻辑功能,如电路板硬件管理,转换为特定PLD的配置位流,用于配置可编程功能单元和互连。配置位流被存储在可编程逻辑器件的片上配置闪存。当电路板上电后,配置闪存中的内容被自动传输到其片上配置SRAM,从而配置可编程功能单元执行所需的硬件管理任务。更新硬件管理功能,可使用不同的位流通过后台随时加载到配置闪存,无需中断可编程逻辑器件正在执行的硬件管理功能。将新存储到闪存的配置传到片上SRAM,电源重启中断系统的正常运行(图1)。

图1:大多数PLD必须等待电源重启进行重新配置

在配置过程中保持稳定的输出

高可用性系统不能容忍电源重启导致的中断。由于通过可编程逻辑器件的I/O使能板上主ASIC和CPU上的DC-DC转换器和控制复位信号,在重配置过程中可编程逻辑器件的输出需保持不变。需要在PLD重配置时保持输出稳定对于应用设计提出了多项挑战。

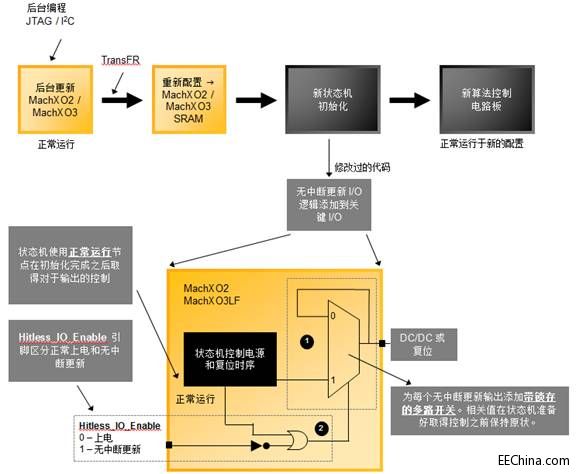

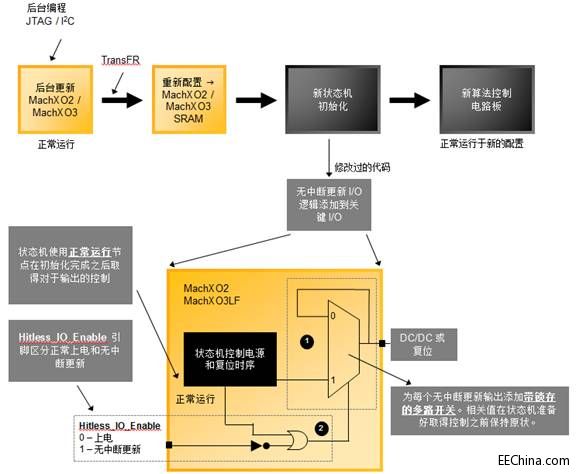

莱迪思MachXO2或MachXO3 PLD系列包括的功能可实现零停机更新(图2)。首先,PLD进行“后台更新” 通过JTAG、SPI或I2C加载新的配置数据到其配置闪存。一旦加载完毕,“TransFR”指令将新的PLD配置从闪存传输到PLD的配置SRAM。执行“TransFR”指令的同时触发了“保持当前状态”功能,确保所有的I/O值在传输过程中保持不变。最后,在“逻辑初始化”步骤,状态机将开始重新启动电源管理并复位电源分配。这将导致电源关断,迫使电路板开始电源上电过程。

图2:采用MachXO2/3无中断更新I/O 的PLD重配置步骤

使用无中断更新I/O解决问题

为了支持零停机更新,PLD器件必须要能够在新镜像创建的状态机处于初始化阶段时,使用于控制电源以及其他逻辑信号的输出保持不变。新算法经过初始化之后,它们将取得对于电源和其他逻辑信号的控制。

为了使得关键I/O在初始化过程中保持原状,用户设计中需要添加“无中断更新I/O”。如图3所示,这需要为每个关键的输出添加一个带锁存的多路开关。该带锁存的多路开关在状态机初始化过程中将输出保持为最后的已知状态,并在初始化过程完成之后将输出控制交还给状态机。该电路能够使用“Hitless_IO_Enable”输入区分正常(上电)启动和重新配置,可避免在正常的上电过程中发生关键输出I/O值被锁死的情况。

深入探讨

图3说明了无中断更新I/O在状态机初始化过程中,在新配置被加载到MachXO2/XO3器件配置SRAM时发挥的作用。

图3:无中断更新I/O在初始化期间使得关键I/O保持最后已知状态

为每个输出添加一个带锁存的多路开关,只要多路开关控制输入为“0”,输出就保持当前值不变。这就意味着无论状态机的输出状态如何,DC-DC转换器保持“on”(如果先前处于“on”的状态)。当控制信号为逻辑值“1”时,DC-DC转换器的状态由状态机控制。状态机通过“正常运行”节点控制多路开关输出。芯片最新添加的“Hitless_IO_Enable”输入可区分正常的“上电”配置(状态机初始化过程中DC-DC转换器输出受到控制)和无中断重新配置流程(状态机初始化过程中DC-DC转换器保持不变)。

假设控制无中断更新流程的“Hitless_IO_Enable”信号设为“1”。

在初始化之前,状态机将“正常运行”信号重设为“0”。带锁存的多路开关将忽略来自状态机的输出,并且DC-DC转换器的“Enable”信号保持不变。

当PLD的逻辑准备好恢复正常运行时,它将“正常运行”信号设为逻辑值“1”(高电平),允许其取得对于DC-DC转换器的控制。此时电路板的DC-DC转换器和复位由更新的电源和复位控制状态机控制。

实际案例

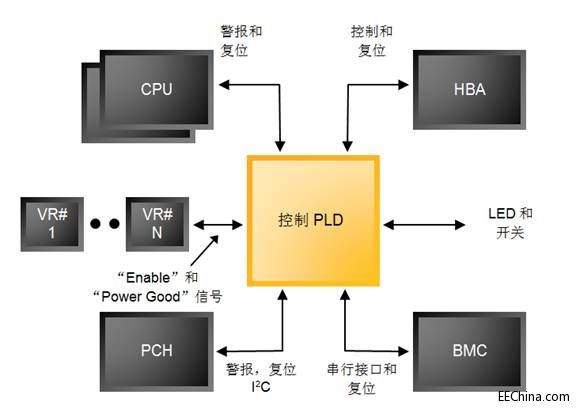

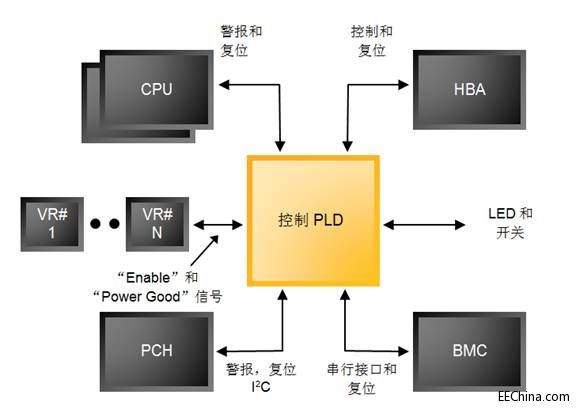

图4中的框图说明了PLD的使用情景,用于对CPU集群(cluster)以及平台控制中心(Platform Controller Hub, PCH)、底板管理控制器(Baseboard Management Controller, BMC)和主机总线适配器(Host Bus Adapter, HBA)等板级子系统进行供电、监控和管理。在此例中,PLD主要负责电路板负载点调压器的上电和断电时序,并在电源重启时将复位和控制信号保持为合适的状态。在正常运行期间,PLD监控子系统的报警参数(温度、电压、存储器和I/O故障等)或状态变化,同时将控制信号稳定保持在合适的状态。

图4:集成在PLD内适用于机架式服务器的控制/内务处理功能

BMC在后台升级服务器的控制PLD并触发“TransFR”指令以使用更新的配置运行PLD。在没有无中断更新I/O的情况下,控制和复位信号或是VR(调压器)信号不能在初始化步骤中保持不变。例如,如果CPU或其外设上的复位信号在重配置过程中发生变化,将导致无论CPU在执行何种功能,都将重新初始化并开始重启流程。同样的,如果“Power Enable”信号变化了,调压器或负载点的电源将被关断,导致由该调压器供电的器件进入未知状态。这会导致电路板中止运行、丢失或扰乱数据,甚至对电路板的电子元器件造成物理损害。

为关键信号添加无中断更新I/O机制使得PLD能够在重新配置的过程中冻结外部传感和控制信号。如此,服务器的关键功能在PLD的常规维护和升级过程中不会中断。该功能对于产品开发也很有用,能够缩短调试时间或是在安装机架时构建专用的产品变量。

高可用性系统,如服务器、通信网关和基站等需要持续工作。一旦现场安装后,就需要通过软件升级来增强系统功能和修复错误。因此,这些系统设计需可以在不中断其正常运行的情况下进行系统功能更新。可编程逻辑器件(PLD)常被用于支持在系统设计更新。使用PLD的改进后的设计成本更低、使用更方便、性能更强,使得可编程逻辑器件成为这些系统中理想的板上硬件管理器件,可管理板上DC-DC转换器、监测和控制关键信号、集合串口通信并执行其他内务管理功能。

不可或缺的PLD

PLD包含一系列可编程功能单元。这些单元的配置和互连实现了板上特定的硬件管理功能。通常情况下,一个软件设计工具将某个逻辑功能,如电路板硬件管理,转换为特定PLD的配置位流,用于配置可编程功能单元和互连。配置位流被存储在可编程逻辑器件的片上配置闪存。当电路板上电后,配置闪存中的内容被自动传输到其片上配置SRAM,从而配置可编程功能单元执行所需的硬件管理任务。更新硬件管理功能,可使用不同的位流通过后台随时加载到配置闪存,无需中断可编程逻辑器件正在执行的硬件管理功能。将新存储到闪存的配置传到片上SRAM,电源重启中断系统的正常运行(图1)。

图1:大多数PLD必须等待电源重启进行重新配置

在配置过程中保持稳定的输出

高可用性系统不能容忍电源重启导致的中断。由于通过可编程逻辑器件的I/O使能板上主ASIC和CPU上的DC-DC转换器和控制复位信号,在重配置过程中可编程逻辑器件的输出需保持不变。需要在PLD重配置时保持输出稳定对于应用设计提出了多项挑战。

莱迪思MachXO2或MachXO3 PLD系列包括的功能可实现零停机更新(图2)。首先,PLD进行“后台更新” 通过JTAG、SPI或I2C加载新的配置数据到其配置闪存。一旦加载完毕,“TransFR”指令将新的PLD配置从闪存传输到PLD的配置SRAM。执行“TransFR”指令的同时触发了“保持当前状态”功能,确保所有的I/O值在传输过程中保持不变。最后,在“逻辑初始化”步骤,状态机将开始重新启动电源管理并复位电源分配。这将导致电源关断,迫使电路板开始电源上电过程。

图2:采用MachXO2/3无中断更新I/O 的PLD重配置步骤

使用无中断更新I/O解决问题

为了支持零停机更新,PLD器件必须要能够在新镜像创建的状态机处于初始化阶段时,使用于控制电源以及其他逻辑信号的输出保持不变。新算法经过初始化之后,它们将取得对于电源和其他逻辑信号的控制。

为了使得关键I/O在初始化过程中保持原状,用户设计中需要添加“无中断更新I/O”。如图3所示,这需要为每个关键的输出添加一个带锁存的多路开关。该带锁存的多路开关在状态机初始化过程中将输出保持为最后的已知状态,并在初始化过程完成之后将输出控制交还给状态机。该电路能够使用“Hitless_IO_Enable”输入区分正常(上电)启动和重新配置,可避免在正常的上电过程中发生关键输出I/O值被锁死的情况。

深入探讨

图3说明了无中断更新I/O在状态机初始化过程中,在新配置被加载到MachXO2/XO3器件配置SRAM时发挥的作用。

图3:无中断更新I/O在初始化期间使得关键I/O保持最后已知状态

为每个输出添加一个带锁存的多路开关,只要多路开关控制输入为“0”,输出就保持当前值不变。这就意味着无论状态机的输出状态如何,DC-DC转换器保持“on”(如果先前处于“on”的状态)。当控制信号为逻辑值“1”时,DC-DC转换器的状态由状态机控制。状态机通过“正常运行”节点控制多路开关输出。芯片最新添加的“Hitless_IO_Enable”输入可区分正常的“上电”配置(状态机初始化过程中DC-DC转换器输出受到控制)和无中断重新配置流程(状态机初始化过程中DC-DC转换器保持不变)。

假设控制无中断更新流程的“Hitless_IO_Enable”信号设为“1”。

在初始化之前,状态机将“正常运行”信号重设为“0”。带锁存的多路开关将忽略来自状态机的输出,并且DC-DC转换器的“Enable”信号保持不变。

当PLD的逻辑准备好恢复正常运行时,它将“正常运行”信号设为逻辑值“1”(高电平),允许其取得对于DC-DC转换器的控制。此时电路板的DC-DC转换器和复位由更新的电源和复位控制状态机控制。

实际案例

图4中的框图说明了PLD的使用情景,用于对CPU集群(cluster)以及平台控制中心(Platform Controller Hub, PCH)、底板管理控制器(Baseboard Management Controller, BMC)和主机总线适配器(Host Bus Adapter, HBA)等板级子系统进行供电、监控和管理。在此例中,PLD主要负责电路板负载点调压器的上电和断电时序,并在电源重启时将复位和控制信号保持为合适的状态。在正常运行期间,PLD监控子系统的报警参数(温度、电压、存储器和I/O故障等)或状态变化,同时将控制信号稳定保持在合适的状态。

图4:集成在PLD内适用于机架式服务器的控制/内务处理功能

BMC在后台升级服务器的控制PLD并触发“TransFR”指令以使用更新的配置运行PLD。在没有无中断更新I/O的情况下,控制和复位信号或是VR(调压器)信号不能在初始化步骤中保持不变。例如,如果CPU或其外设上的复位信号在重配置过程中发生变化,将导致无论CPU在执行何种功能,都将重新初始化并开始重启流程。同样的,如果“Power Enable”信号变化了,调压器或负载点的电源将被关断,导致由该调压器供电的器件进入未知状态。这会导致电路板中止运行、丢失或扰乱数据,甚至对电路板的电子元器件造成物理损害。

为关键信号添加无中断更新I/O机制使得PLD能够在重新配置的过程中冻结外部传感和控制信号。如此,服务器的关键功能在PLD的常规维护和升级过程中不会中断。该功能对于产品开发也很有用,能够缩短调试时间或是在安装机架时构建专用的产品变量。

半导体 电路 电源管理 总线 电压 电子 CPLD 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA 上同步开关噪声的分析(04-05)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)