Xilinx FPGA入门连载63:基于数码管显示的RTC读取之RTC芯片解析

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

本实例使用的RTC实时时钟芯片是型号为PCF8563,是PHILIPS 公司推出的一款工业级内含IIC 总线接口功能的具有极低功耗的多功能时钟/日历芯片。PCF8563的多种报警功能、定时器功能、时钟输出功能以及中断输出功能能完成各种复杂的定时服务,甚至可为单片机提供看门狗功能。内部时钟电路、内部振荡电路、内部低电压检测电路(1.0V) 以

及两线制IIC 总线通讯方式,不但使外围电路及其简洁,而且也增加了芯片的可靠性。同时每次读写数据后内嵌的字地址寄存器会自动产生增量,因而PCF8563 是一款性价比极高的时钟芯片,它已被广泛用于电表、水表、气表、电话、传真机、便携式仪器以及电池供电的仪器仪表等产品领域。

特性

● 宽电压范围1.0 5.5V 复位电压标准值Vlow=0.9V

● 超低功耗典型值为0.25 A VDD=3.0V,Tamb=25°C

● 可编程时钟输出频率为32.768KHz/1024Hz/32Hz/1Hz

● 四种报警功能和定时器功能

● 内含复位电路振荡器电容和掉电检测电路

● 开漏中断输出

● 400kHz的IIC 总线(VDD=1.8-5.5V) 其从地址读0xa3,写0xa2

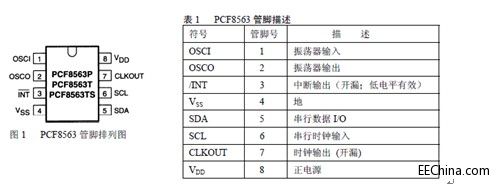

PCF8563的引脚排列及描述如下所示。

PCF8563有16 个位寄存器:一个可自动增量的地址寄存器,一个内置32.768KHz 的振荡器(带有一个内部集成的电容),一个分频器用于给实时时钟RTC 提供源时钟,一个可编程时钟输出,一个定时器,一个报警器,一个掉电检测器和一个400KHz的IIC 总线接口。

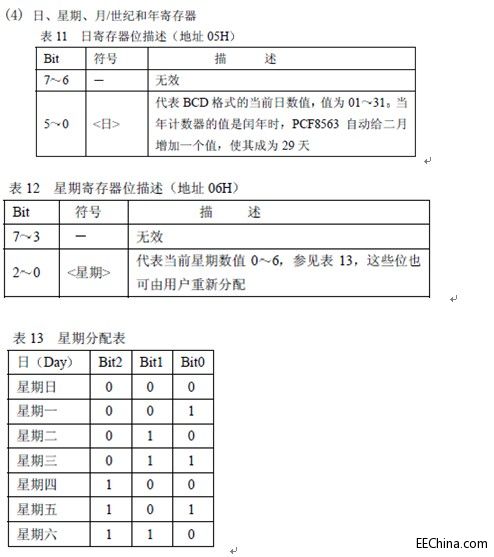

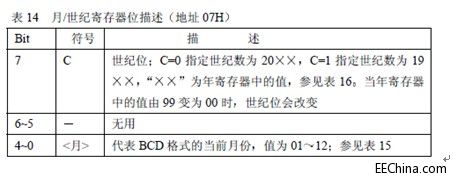

所有 16 个寄存器设计成可寻址的8 位并行寄存器,但不是所有位都有用。前两个寄存器(内存地址00H 01H)用于控制寄存器和状态寄存器,内存地址02H~08H 用于时钟计数器(秒~年计数器),地址09H~0CH用于报警寄存器(定义报警条件),地址0DH 控制CLKOUT 引脚的输出频率,地址0EH 和0FH分别用于定时器控制寄存器和定时器寄存器。秒、分钟、小时、日、月、年、分钟报警、小时报警、日报警寄存器,编码格式为BCD,星期和星期报警寄存器不以BCD 格式编码。

当一个 RTC 寄存器被读时,所有计数器的内容被锁存。因此,在传送条件下,可以禁止对时钟日历芯片的错读。

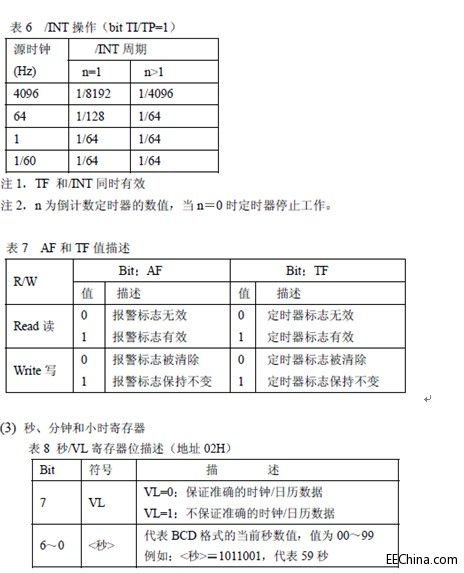

PCF8563 共有16 个寄存器,其中00H~01H为控制方式寄存器;09H~0CH为报警功能寄存器;0DH为时钟输出寄存器;0EH 和0FH 为定时器功能寄存器,02H~08H为秒~年时间寄存器。各寄存器的位描述如下示。

看了这么多条条框框的寄存器描述,大家一定有些累了,下面我们来电实用的,和大家简单说说如何使用这个芯片初始设置或读出年月日时分秒等信息。

我们将并且只能够使用IIC接口来读写这个芯片的各个寄存器,IIC接口有一定的协议,需要按照协议规定送起始位、器件地址、读写寄存器地址、读写数据、停止位等,这个内容我们下一小节的设计中详细探讨,后面我们先抛开IIC具体读写控制时序,先从宏观角度来把该读写哪些寄存器这码事理清楚。

正常来说,一个芯片的使用,无外乎设置一下控制寄存器,然后读写相关数据,必要的话产生一个中断,此时可能回去看看状态寄存器。不过,我们这颗RTC更简单,地址0x00和0x01的控制寄存器1和2默认状态即可,我们只需要读写时间便可,其他什么报警、中断等功能留待大家有兴趣自己琢磨去。好,那么简单又是怎么操作的,不急,精彩马上送到。

地址0x02~0x08寄存器的内容是秒、分、时、日、星期、月、年信息,我们只要操作他们便可以了。

假设现在我们就是要把这些基本的时间信息读出来,然后以我们最常规的大家都能看得懂的10进制方式显示出来,那么如何操作?就按下面这个步骤就好,至于原理,大家回去对照各个寄存器的定义稍微一想也就能够领会。

① 读地址0x02的秒寄存器数据second,在显示时,十位数据为((second&0x70)>>4),个位的数据为(second&0x0f)。

② 读地址0x03的分钟寄存器数据minute,在显示时,十位数据为((minute&0x70)>>4),个位的数据为(minute&0x0f)。

③ 读地址0x04的小时寄存器数据hour,在显示时,十位数据为((hour&0x30)>>4),个位的数据为(hour&0x0f)。

④ 读地址0x05的日寄存器数据day,在显示时,十位数据为((day&0x30)>>4),个位的

Xilinx FPGA 总线 单片机 看门狗 电路 电压 振荡器 电容 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)