给MCU工程师详解FPGA硬件属性

时间:03-30

来源:互联网

点击:

更为复杂的FPGA架构

正如我们在前面说的那样,赛灵思公司在1985年推出的第一块FPGA—XC2064包含8×8=64的逻辑块阵列,每个逻辑块包含一个四输入查找表及其它一些简单功能。由于它们的容量非常有限,因此早期的FPGA只用来执行一些相对简单的任务,比如集中一些胶合逻辑,或实现基本的状态机。然而随着时间的推移,事情开始改变……

随着时间的推移和工艺节点的进步,FPGA的容量和性能不断得到提高,功耗却不断的下降。直到大约2006年以前广泛使用的一直是四输入查找表。事实上,在写这篇文章之时,较小的FPGA系列器件仍在使用四输入的查找表,但一些高端器件可能使用六、七或八输入的查找表。这些大家伙可能被用作一个大的查找表,或分裂成许多更小的功能,比如两个四输入的查找表或一个三输入一个五输入的查找表。在实际的高端器件中,这种可编程构造可以描述相当于百万级(有时甚至千万级)的原始逻辑门。

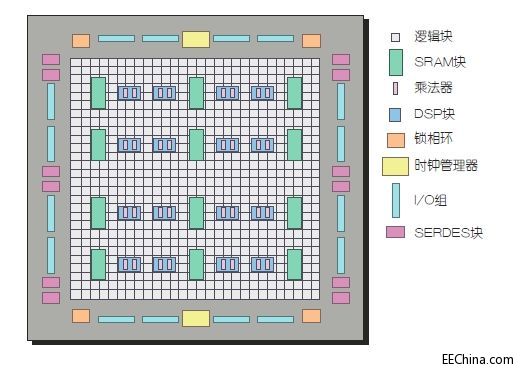

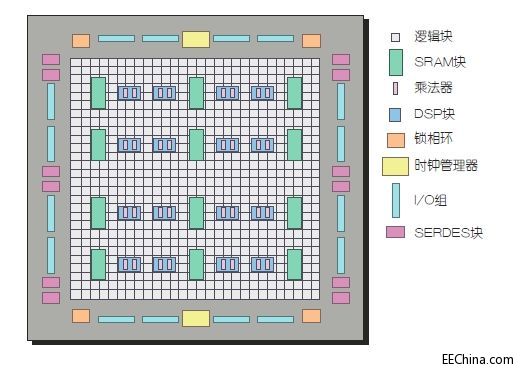

如果某个逻辑功能(比方说计数器)是用FPGA的可编程构造实现的,那么这个功能可以被说成“软功能”。相比之下,如果某个功能是直接用芯片实现的,则被说成“硬功能”。(随着这些功能变得越来越大越来越复杂,我们一般称它们为内核)。软内核的优势在于,你可以让它们做你想让它们做的任何事。硬内核的优势是它们占用较少的硅片面积,具有较高的性能,并且功耗较低。最优的解决方案是混合使用软内核(用可编程构造实现)和硬内核(直接用硅片实现)。这样,除了基于查找表的可编程构造外,今天的FPGA可以利用以下介绍的各种硬内核进行性能增强:

图3:更复杂的FPGA架构。

举例来说,该器件可能包含数千个加法器、乘法器和数字信号处理(DSP)功能;数兆位的片上内存,大量的高速串行互连(SERDES)收发器模块,以及众多的其它功能。

带嵌入式处理器的FPGA

这是真正让人兴奋的事情……你可以用FPGA中的普通可编程构造做的事情之一是,使用其中的一部分实现一个或多个软处理器内核。当然,你可以实现不同规模的处理器。举例来说,你可以创建一个或多个8位的处理器,加上一个或多个16位或32位的软处理器—所有处理器都在同一器件中。

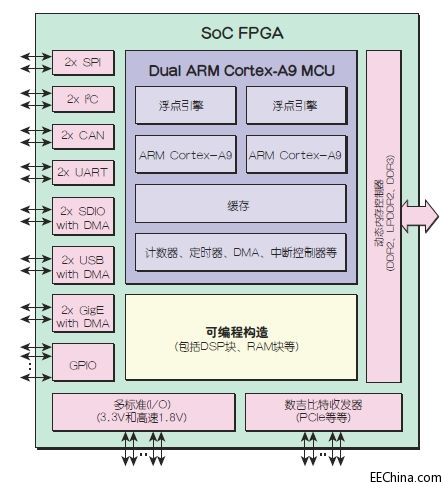

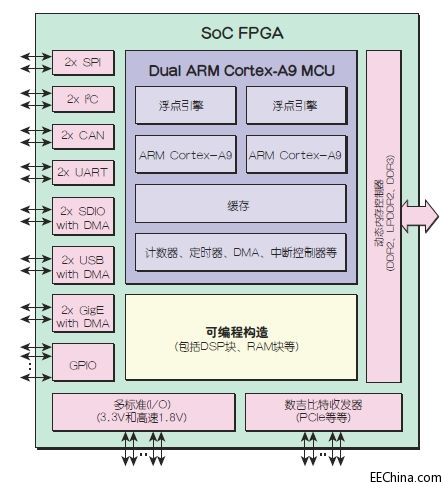

如果FPGA供应商希望提供一个占用较少硅片面积、消耗较低功率但性能更高的处理器,解决方案是将它实现为硬内核。一个非常令人兴奋的开发成果是Altera和赛灵思等公司最近推出的SoC FPGA。考虑下面所示这个例子:

图4:一种新的SoC FPGA

这个漂亮的小东西整合了一个完全以硬内核方式实现的双路ARM Cortex-A9微控制器子系统(运行时钟高达1GHz,包含浮点引擎,片上缓存,计数器,定时器等),以及种类广泛的硬内核接口功能(SPI,I2C,CAN等),还有一个硬内核的动态内存控制器,所有这些组件都利用大量传统的可编程构造和大量的通用输入输出(GPIO)引脚进行了性能增强。(即将在16nm节点推出的一款SoC FPGA据称包含四内核的64位ARM Cortex-A53处理器,双内核32位ARM Cortex-R5实时处理器,以及一个ARM Mali-400MP图形处理器。这些可不是你祖母时候的FPGA哦!)

传统的嵌入式系统架构师可能将其中一个器件放置在电路板上,并将它用作传统的高性能双内核ARM Cortex-A9微控制器。当电路板上电时,硬微控制器内核立即启动,并在任何可编程构造完成配置之前就可用了。这样可以节省时间和精力,并让软件开发人员和硬件设计师同时开始开发。

一种情形是软件开发人员捕获他们的代码,在SoC FPGA的Cortex-A9处理器上运行这些代码,然后通过分析识别任何可能严重影响性能并成为瓶颈的功能。这些功能随后可能就转交给硬件设计工程师用可编程构造来实现,它们(这些功能,不是设计工程师)将使用较低的时钟频率提供明显更高的性能,而且功耗更低。

前面我们说过,硬内核实现的功能(图4所示的ARM Cortex-A9就是一种硬内核)与等效的软内核相比具有更高的性能和更低的功耗。但现在我们又说如果在硬内核处理器上运行的软件功能是个瓶颈,我们可以用可编程构造来实现,这样它就能……你理解的没错,提供更高的性能和更低的功耗。

正如我们在前面说的那样,赛灵思公司在1985年推出的第一块FPGA—XC2064包含8×8=64的逻辑块阵列,每个逻辑块包含一个四输入查找表及其它一些简单功能。由于它们的容量非常有限,因此早期的FPGA只用来执行一些相对简单的任务,比如集中一些胶合逻辑,或实现基本的状态机。然而随着时间的推移,事情开始改变……

随着时间的推移和工艺节点的进步,FPGA的容量和性能不断得到提高,功耗却不断的下降。直到大约2006年以前广泛使用的一直是四输入查找表。事实上,在写这篇文章之时,较小的FPGA系列器件仍在使用四输入的查找表,但一些高端器件可能使用六、七或八输入的查找表。这些大家伙可能被用作一个大的查找表,或分裂成许多更小的功能,比如两个四输入的查找表或一个三输入一个五输入的查找表。在实际的高端器件中,这种可编程构造可以描述相当于百万级(有时甚至千万级)的原始逻辑门。

如果某个逻辑功能(比方说计数器)是用FPGA的可编程构造实现的,那么这个功能可以被说成“软功能”。相比之下,如果某个功能是直接用芯片实现的,则被说成“硬功能”。(随着这些功能变得越来越大越来越复杂,我们一般称它们为内核)。软内核的优势在于,你可以让它们做你想让它们做的任何事。硬内核的优势是它们占用较少的硅片面积,具有较高的性能,并且功耗较低。最优的解决方案是混合使用软内核(用可编程构造实现)和硬内核(直接用硅片实现)。这样,除了基于查找表的可编程构造外,今天的FPGA可以利用以下介绍的各种硬内核进行性能增强:

图3:更复杂的FPGA架构。

举例来说,该器件可能包含数千个加法器、乘法器和数字信号处理(DSP)功能;数兆位的片上内存,大量的高速串行互连(SERDES)收发器模块,以及众多的其它功能。

带嵌入式处理器的FPGA

这是真正让人兴奋的事情……你可以用FPGA中的普通可编程构造做的事情之一是,使用其中的一部分实现一个或多个软处理器内核。当然,你可以实现不同规模的处理器。举例来说,你可以创建一个或多个8位的处理器,加上一个或多个16位或32位的软处理器—所有处理器都在同一器件中。

如果FPGA供应商希望提供一个占用较少硅片面积、消耗较低功率但性能更高的处理器,解决方案是将它实现为硬内核。一个非常令人兴奋的开发成果是Altera和赛灵思等公司最近推出的SoC FPGA。考虑下面所示这个例子:

图4:一种新的SoC FPGA

这个漂亮的小东西整合了一个完全以硬内核方式实现的双路ARM Cortex-A9微控制器子系统(运行时钟高达1GHz,包含浮点引擎,片上缓存,计数器,定时器等),以及种类广泛的硬内核接口功能(SPI,I2C,CAN等),还有一个硬内核的动态内存控制器,所有这些组件都利用大量传统的可编程构造和大量的通用输入输出(GPIO)引脚进行了性能增强。(即将在16nm节点推出的一款SoC FPGA据称包含四内核的64位ARM Cortex-A53处理器,双内核32位ARM Cortex-R5实时处理器,以及一个ARM Mali-400MP图形处理器。这些可不是你祖母时候的FPGA哦!)

传统的嵌入式系统架构师可能将其中一个器件放置在电路板上,并将它用作传统的高性能双内核ARM Cortex-A9微控制器。当电路板上电时,硬微控制器内核立即启动,并在任何可编程构造完成配置之前就可用了。这样可以节省时间和精力,并让软件开发人员和硬件设计师同时开始开发。

一种情形是软件开发人员捕获他们的代码,在SoC FPGA的Cortex-A9处理器上运行这些代码,然后通过分析识别任何可能严重影响性能并成为瓶颈的功能。这些功能随后可能就转交给硬件设计工程师用可编程构造来实现,它们(这些功能,不是设计工程师)将使用较低的时钟频率提供明显更高的性能,而且功耗更低。

前面我们说过,硬内核实现的功能(图4所示的ARM Cortex-A9就是一种硬内核)与等效的软内核相比具有更高的性能和更低的功耗。但现在我们又说如果在硬内核处理器上运行的软件功能是个瓶颈,我们可以用可编程构造来实现,这样它就能……你理解的没错,提供更高的性能和更低的功耗。

嵌入式 MCU FPGA 集成电路 场效应管 电路 电压 赛灵思 DSP 收发器 Altera SoC ARM Cortex 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)