关于边沿检测简单理解

时间:05-10

来源:互联网

点击:

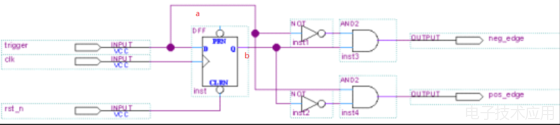

1、所谓边沿检测,就是检测输入信号或FPGA内部逻辑信号电平的跳变,即实现上升沿或下降沿的检测,捕获到以后以此用作使能信号(简单可理解为:一旦检测到这个信号,则发生什么什么),来作为时序逻辑的触发信号。总之,在基础中,这个还是很重要的,在后面的串口和SPI接口中都要用到。

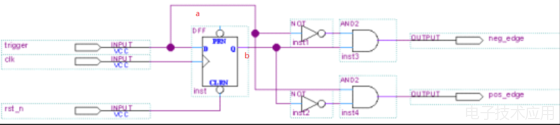

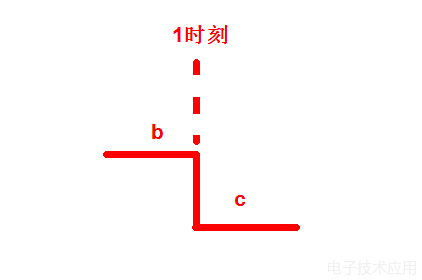

(一)、一级寄存器

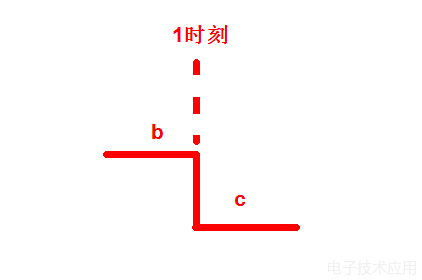

从一级寄存器中很好理解下降沿和上升沿的检测:a和b都是从trigger来的(三者一样),只是b比a在时间上迟了一个寄存器的时间。现在假设0时刻到了,trigger到a了,但是还没有到b,到了寄存器,被寄存了;等待下一个时刻1到来,a走了(不用管了),来了一个新的叫c,同时,b从寄存器得到了之前寄存的,那个现在的1时刻,有了两个信号,b和c,而且b是前一个时刻的,而c是现在时刻的(谁先谁后这点很重要)。所以:

下降沿 neg_edge = b & ~c;

由上图可以看出,当下降沿来的时候,c取反再与上b,得出输出为1;反过来想,输出neg_edge为1的时候就表示检测到下降沿了。

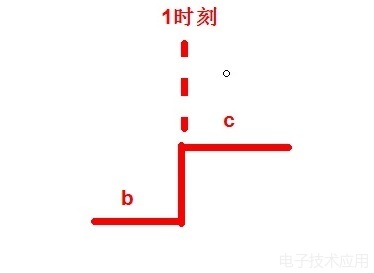

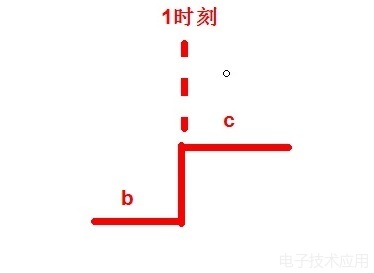

上升沿 pos_edge = ~b & c;

同理。当pos_edge为1,表示检测到上升沿。

(二)两级寄存器

moduleedge_tech_design

(

clk,

rst_n,

s,

neg_edge,

pos_edge

);

inputclk;

inputrst_n;

inputs;

outputneg_edge;

outputpos_edge;

regc,d;

always@(posedgeclkornegedgerst_n)

if(!rst_n)begin

c

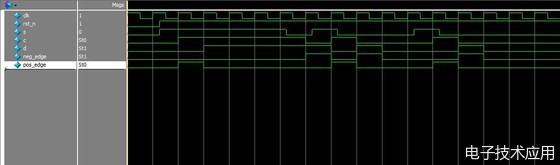

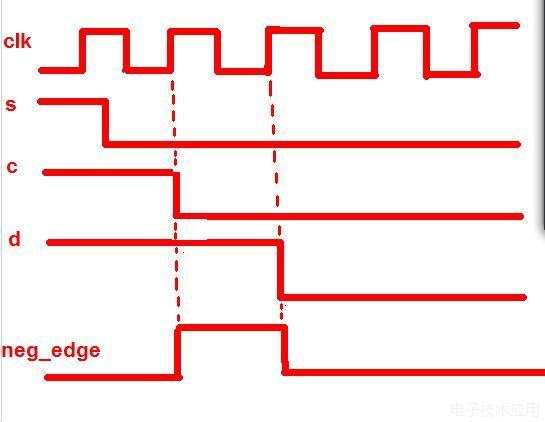

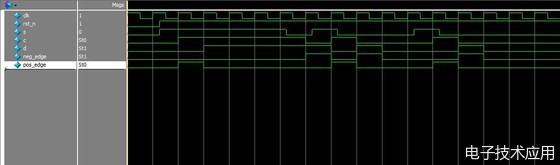

在仿真图中可以看到这样的图形(街区图中下降沿部分一小段)

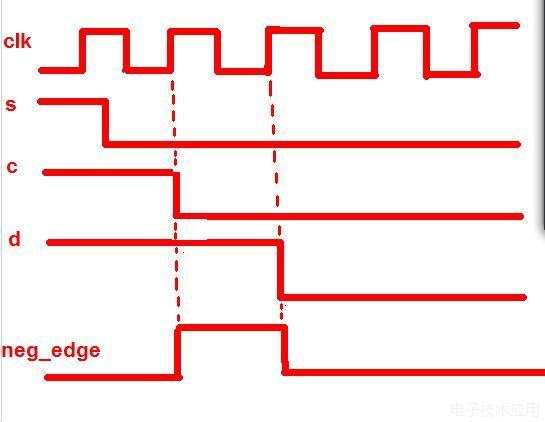

输入信号s从高变成低的时候,出现下降沿,然后等到时钟clk的上升沿到来,s传输到c,d还没传输到,被寄存在d之前的寄存器内,等待第二个时钟上升沿到来,寄存器中的信号传输到d了,此时根据

neg_edge = d & ~c;

可以得到neg_edge的波形。

(一)、一级寄存器

从一级寄存器中很好理解下降沿和上升沿的检测:a和b都是从trigger来的(三者一样),只是b比a在时间上迟了一个寄存器的时间。现在假设0时刻到了,trigger到a了,但是还没有到b,到了寄存器,被寄存了;等待下一个时刻1到来,a走了(不用管了),来了一个新的叫c,同时,b从寄存器得到了之前寄存的,那个现在的1时刻,有了两个信号,b和c,而且b是前一个时刻的,而c是现在时刻的(谁先谁后这点很重要)。所以:

下降沿 neg_edge = b & ~c;

由上图可以看出,当下降沿来的时候,c取反再与上b,得出输出为1;反过来想,输出neg_edge为1的时候就表示检测到下降沿了。

上升沿 pos_edge = ~b & c;

同理。当pos_edge为1,表示检测到上升沿。

(二)两级寄存器

moduleedge_tech_design

(

clk,

rst_n,

s,

neg_edge,

pos_edge

);

inputclk;

inputrst_n;

inputs;

outputneg_edge;

outputpos_edge;

regc,d;

always@(posedgeclkornegedgerst_n)

if(!rst_n)begin

c

在仿真图中可以看到这样的图形(街区图中下降沿部分一小段)

输入信号s从高变成低的时候,出现下降沿,然后等到时钟clk的上升沿到来,s传输到c,d还没传输到,被寄存在d之前的寄存器内,等待第二个时钟上升沿到来,寄存器中的信号传输到d了,此时根据

neg_edge = d & ~c;

可以得到neg_edge的波形。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)