零基础学FPGA (二十五)必会! 从静态时序分析到SDRAM时序收敛(下篇)

时间:01-28

来源:互联网

点击:

八、多周期约束

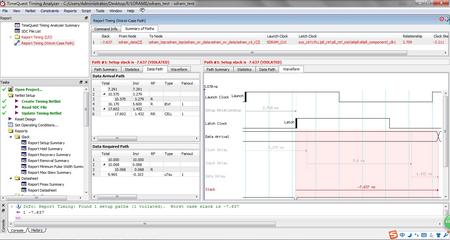

对其进行全编译,查看时序报告,发现时序仍然不收敛

查看错误时序报告可以看到,我们没有做多周期约束,至于为什么,上面已经说过了,这里直接来做

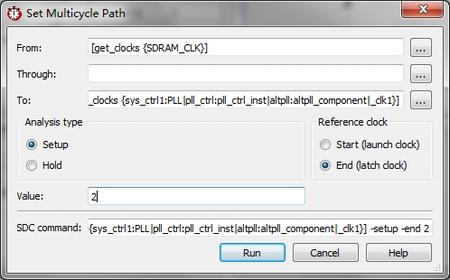

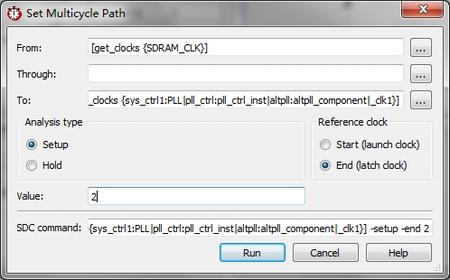

我们设置延时周期数为2,即在第二个时钟周期进行数据锁存,因为是输入路径时序违规,所以我们约束的多周期路径就是从我们的虚拟时钟,也就是SDRAM的工作时钟,到我们FPGA的工作时钟clk1

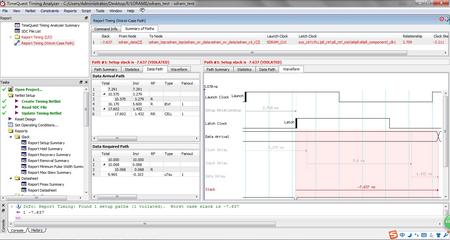

再执行一次全编译,所有的路径达到时序收敛

当然,除了这些,我们还需要一些时序上的优化,以及一些微调,要想达到系统的真正稳定,光做这些还是不够的,小墨也是在学习当中,更深入的探究我只能说对于现在的我来说是力不从心了,有很多经验都是我们后续在不断地摸索中获得的,急也没用,还是安心做好当下,一步一个脚印,学无止境,我们永远不能说自己学会了,只能说熟悉了,慢慢来吧~大家还需加油!

下面是我调好的板级测试图,下面也会附有源代码,不过下到你的板子上不一定跑的起来哦,大家还是自己亲手算算这些参数,等到板子真正跑起来的时候,你才会感受到那种成功的喜悦~

好了,SDRAM就写到这吧,谢谢大家的支持~

对其进行全编译,查看时序报告,发现时序仍然不收敛

查看错误时序报告可以看到,我们没有做多周期约束,至于为什么,上面已经说过了,这里直接来做

我们设置延时周期数为2,即在第二个时钟周期进行数据锁存,因为是输入路径时序违规,所以我们约束的多周期路径就是从我们的虚拟时钟,也就是SDRAM的工作时钟,到我们FPGA的工作时钟clk1

再执行一次全编译,所有的路径达到时序收敛

当然,除了这些,我们还需要一些时序上的优化,以及一些微调,要想达到系统的真正稳定,光做这些还是不够的,小墨也是在学习当中,更深入的探究我只能说对于现在的我来说是力不从心了,有很多经验都是我们后续在不断地摸索中获得的,急也没用,还是安心做好当下,一步一个脚印,学无止境,我们永远不能说自己学会了,只能说熟悉了,慢慢来吧~大家还需加油!

下面是我调好的板级测试图,下面也会附有源代码,不过下到你的板子上不一定跑的起来哦,大家还是自己亲手算算这些参数,等到板子真正跑起来的时候,你才会感受到那种成功的喜悦~

好了,SDRAM就写到这吧,谢谢大家的支持~

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)