SignalTap II Logic Analyzer

时间:02-17

来源:互联网

点击:

一、为啥别忘了我

嵌入式逻辑分析仪—SigbalTap II,是Altera Quartus II 自带的嵌入式逻辑分析仪,与Modelsim软件仿真有所不同,是在线式的仿真,更准确的观察数据的变化,方便调试。

很多学过单片机的孩子认为,单片机可以在线单步调试,而FPGA是并发的,不能单步调试,这使得FPGA的调试学习带来了困难。其实这个说法不是完全正确的。别忘了,还有SignalTap II Logic Analyzer。有了这个嵌入式逻辑分析仪,在调试多通道或单通道数据,进行数据采样、监控等操作时,给我们带来了很大的方便,因此,FPGA的学习中,利用JTAG来调试SiganlTap II将会有很大的帮助。

二、应用实例

本例中用正弦波、三角波、锯齿波、方波波形数据为参考,简要讲解SignalTap II Logic Analyzer软件的应用,步骤如下:

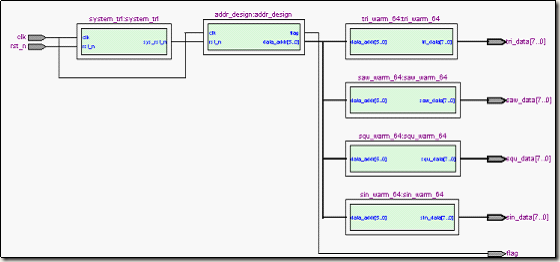

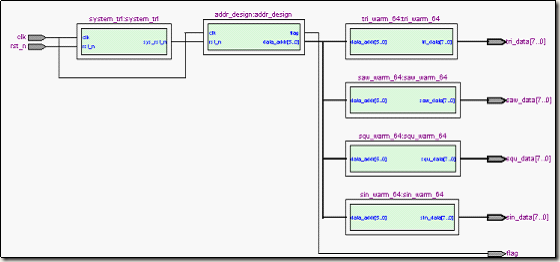

(1)新建工程,设计代码,引脚配置,RTL图如下

(2)新建SignalTap II 文件

(3) 设置待测信号名

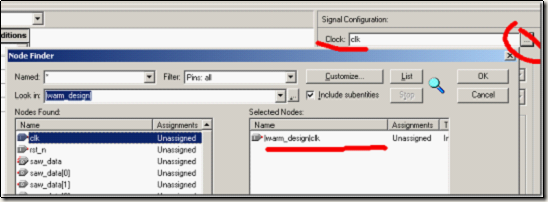

(4)在node双击添加需要观察的数字信号;不要调入系统时钟,因为本例打算用系统时钟来做逻辑分析仪的采样时钟

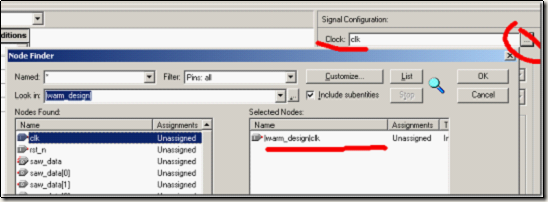

(5)添加系统采样时钟(类似示波器的采样)

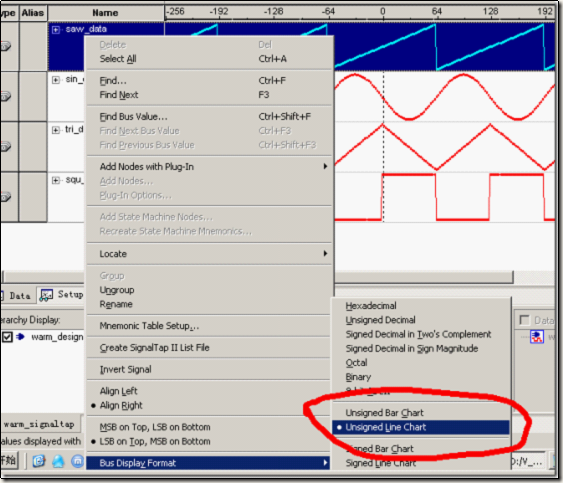

(6)设置采样深度:因为占用ESB/M9K,采样深度最好小于9K,这里设置为2K

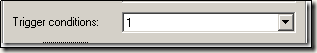

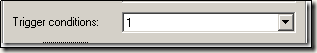

(7)设置采样其实触发位置:跳变沿触发

(8)触发方式:

(此处我也不是很清楚,大概各种模式吧)

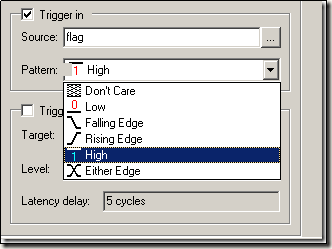

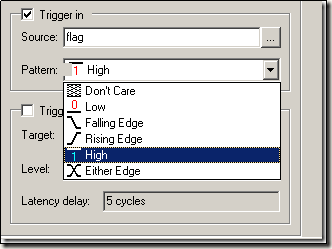

(9)设置触发输入:选择触发信号以及触发方式,flag为触发使能信号,实际工程中没用,只是signaltap ii的使能信号;高电平触发,设置如下:

注意:flag为边沿采样信号,当flag变化的时候,恰好warm_data在稳态,因此将flag作为采样的触发;当然在低速地要求的情况下,flag也可以省略,SiganlTap II 会自动根据一定频率采样。

(10)Save and Yes,再次编译,和本工程捆绑在一起Download to Device,(当然也可以在Settings设置);关于PIN,如果没有逻辑分析仪测试没有信号输入,如果你懒得设置,可以不分配out的信号,但是clk和rst_n必须分配,因为那是系统的驱动信号。

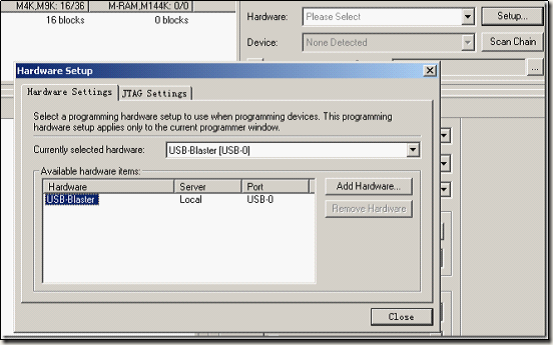

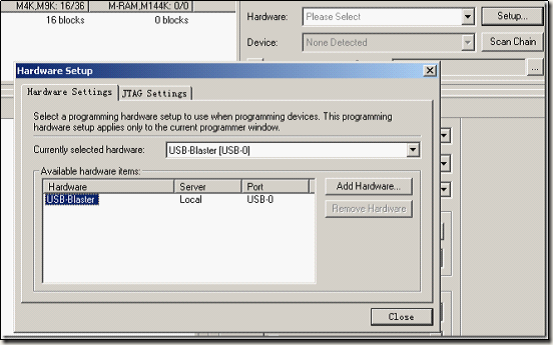

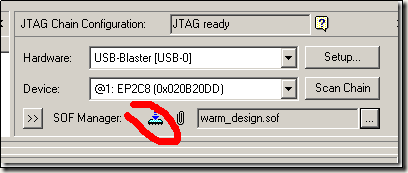

(11)设置Handware Setup,链接Device

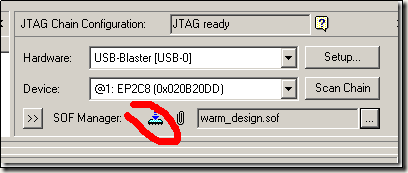

(12)Download sof文件(当然也可以在Q II直接download)

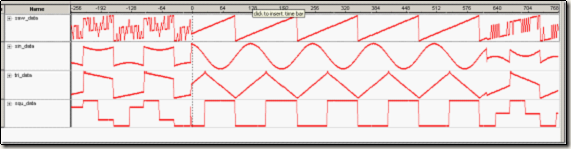

(13)进程—Anturon Analysis,自动分析

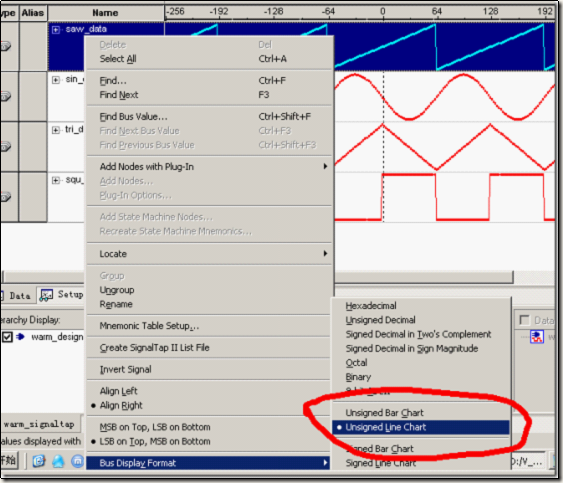

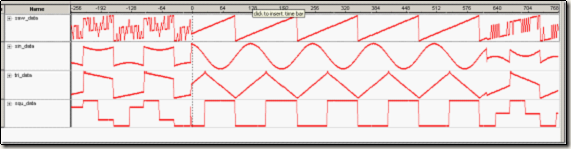

(14) 观察输出信号,设置为模拟信号,如下,方便观察

(15)为什么可以那么帅。。。。

(16)实际测试到一段时间后,会出现bug,可能长时间采样倒是逻辑边沿不能对齐吧,毕竟没那么完美,复位一下就好了。

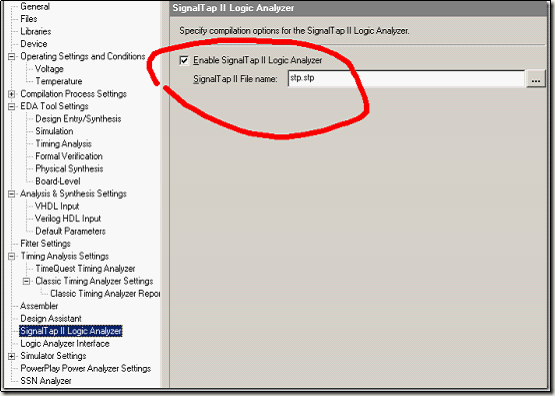

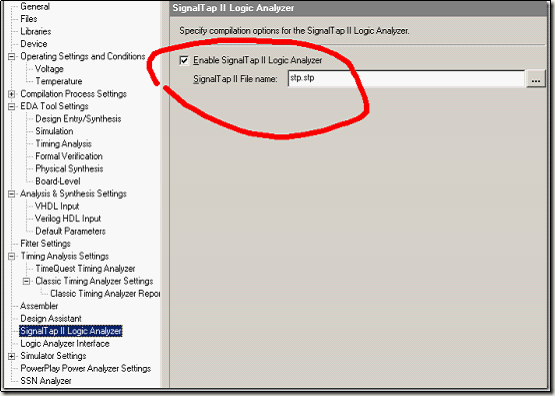

(17)测试ok 后,取消下图中的enable SignalTap II Logic Analyzer ,减少逻辑单元,精简成本设计:

(17) OK ,白白,Just Try,Try,Try。。。。

嵌入式逻辑分析仪—SigbalTap II,是Altera Quartus II 自带的嵌入式逻辑分析仪,与Modelsim软件仿真有所不同,是在线式的仿真,更准确的观察数据的变化,方便调试。

很多学过单片机的孩子认为,单片机可以在线单步调试,而FPGA是并发的,不能单步调试,这使得FPGA的调试学习带来了困难。其实这个说法不是完全正确的。别忘了,还有SignalTap II Logic Analyzer。有了这个嵌入式逻辑分析仪,在调试多通道或单通道数据,进行数据采样、监控等操作时,给我们带来了很大的方便,因此,FPGA的学习中,利用JTAG来调试SiganlTap II将会有很大的帮助。

二、应用实例

本例中用正弦波、三角波、锯齿波、方波波形数据为参考,简要讲解SignalTap II Logic Analyzer软件的应用,步骤如下:

(1)新建工程,设计代码,引脚配置,RTL图如下

(2)新建SignalTap II 文件

(3) 设置待测信号名

(4)在node双击添加需要观察的数字信号;不要调入系统时钟,因为本例打算用系统时钟来做逻辑分析仪的采样时钟

(5)添加系统采样时钟(类似示波器的采样)

(6)设置采样深度:因为占用ESB/M9K,采样深度最好小于9K,这里设置为2K

(7)设置采样其实触发位置:跳变沿触发

(8)触发方式:

(此处我也不是很清楚,大概各种模式吧)

(9)设置触发输入:选择触发信号以及触发方式,flag为触发使能信号,实际工程中没用,只是signaltap ii的使能信号;高电平触发,设置如下:

注意:flag为边沿采样信号,当flag变化的时候,恰好warm_data在稳态,因此将flag作为采样的触发;当然在低速地要求的情况下,flag也可以省略,SiganlTap II 会自动根据一定频率采样。

(10)Save and Yes,再次编译,和本工程捆绑在一起Download to Device,(当然也可以在Settings设置);关于PIN,如果没有逻辑分析仪测试没有信号输入,如果你懒得设置,可以不分配out的信号,但是clk和rst_n必须分配,因为那是系统的驱动信号。

(11)设置Handware Setup,链接Device

(12)Download sof文件(当然也可以在Q II直接download)

(13)进程—Anturon Analysis,自动分析

(14) 观察输出信号,设置为模拟信号,如下,方便观察

(15)为什么可以那么帅。。。。

(16)实际测试到一段时间后,会出现bug,可能长时间采样倒是逻辑边沿不能对齐吧,毕竟没那么完美,复位一下就好了。

(17)测试ok 后,取消下图中的enable SignalTap II Logic Analyzer ,减少逻辑单元,精简成本设计:

(17) OK ,白白,Just Try,Try,Try。。。。

嵌入式 Altera Quartus 仿真 单片机 FPGA 示波器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)