玩转Vivado之Simulation

特权同学,版权所有

1. 可用于Testbench分类管理的Simulation Sets

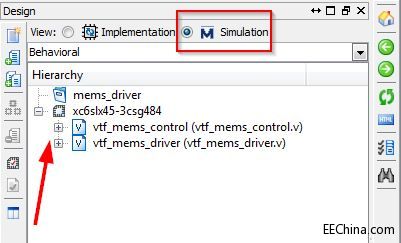

关于Simulation的文件管理,ISE和Vivado的视窗大同小异。ISE可以添加多个不同的testbench文件,也可以自动识别和被测试源文件的层次关系,如图1所示。

图1 ISE中testbench文件管理

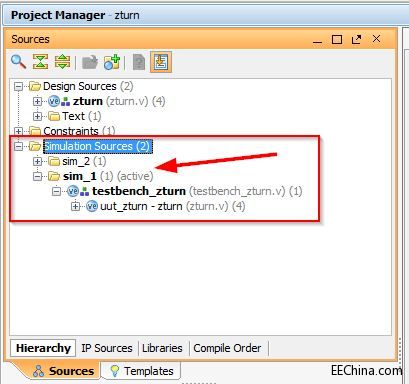

Vivado中对于testbench的管理,增加了一个sets的概念,类似不同的文件夹,如同图2中的sim_1和sim_2,这对于管理不同的testbench,如行为仿真用一个testbench、时序仿真用一个testbench,或者不同的子模块都需要分别由各自的testbench,分类管理更一目了然。

图2 Vivado中testbench文件管理

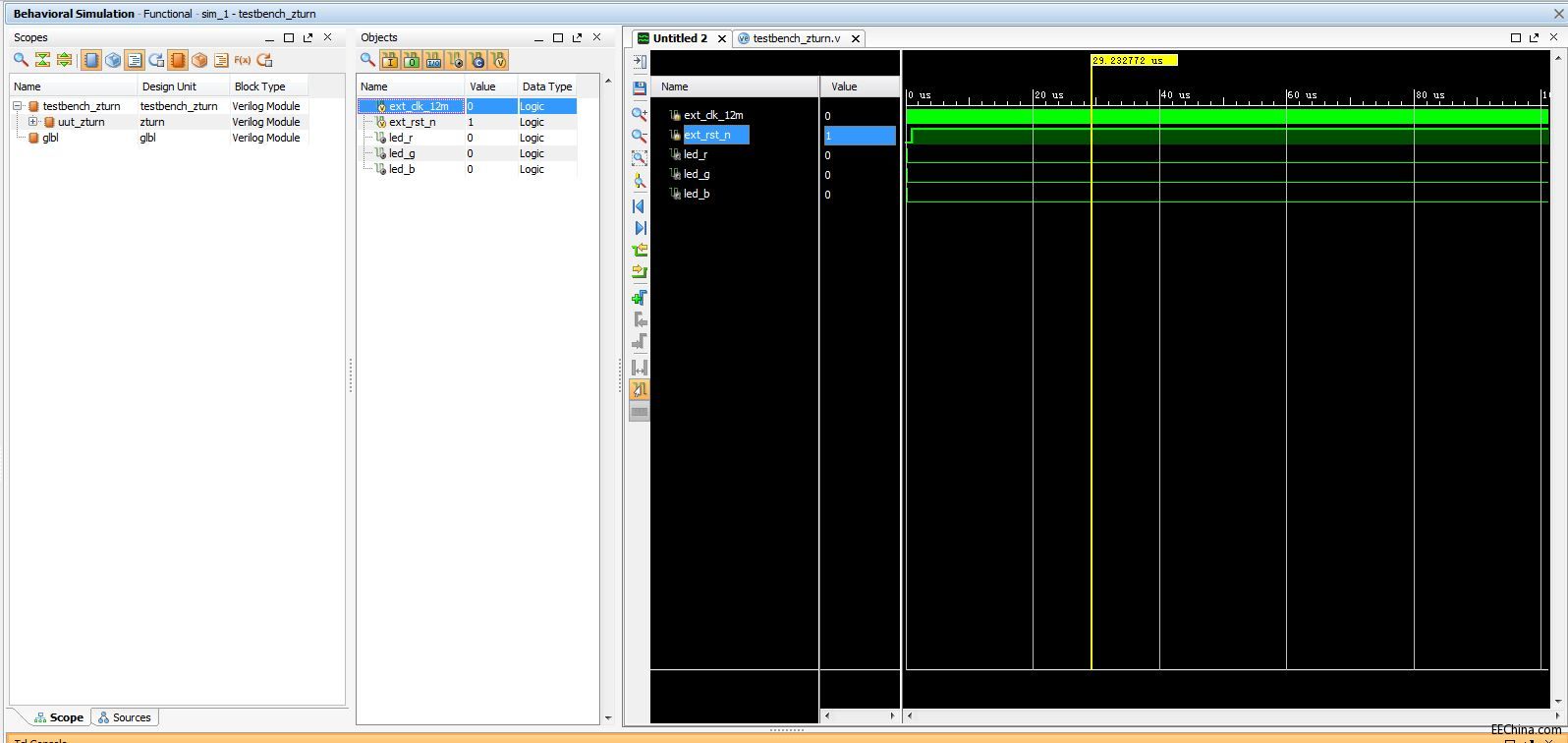

2. Vivado自带的Simulation/Simulator工具

与Altera索性放弃自己的内置simulation工具转而直接与Modelsim合作推出Altera-Modelsim作为首选的第三方仿真工具不同,Xilinx还在用心的维护着自己的simulation(Simulator)工具,虽然从感受上看,有Modelsim的影子,但还是略显“单薄”了,做些入门实验或简单的逻辑功能还凑合,稍微复杂些的应用用它simulation可能就难以招架了。当然,既然如此,Xilinx为什么还要留着这个“鸡肋”,恐怕有他自己的考虑,咱就不多加揣测了。

图3 Vivado自带的Simulation/Simulator工具

2. 第三方仿真工具支持

关于第三方仿真工具的支持,官方ug中提到能够支持以下工具,但是实测Modelsim SE也能够支持。

Thefollowing third-party tools are supported:

•QuestaSim

•ModelSim (PE and DE)

• IES

• VCS

• Riviera PRO simulator (Aldec)

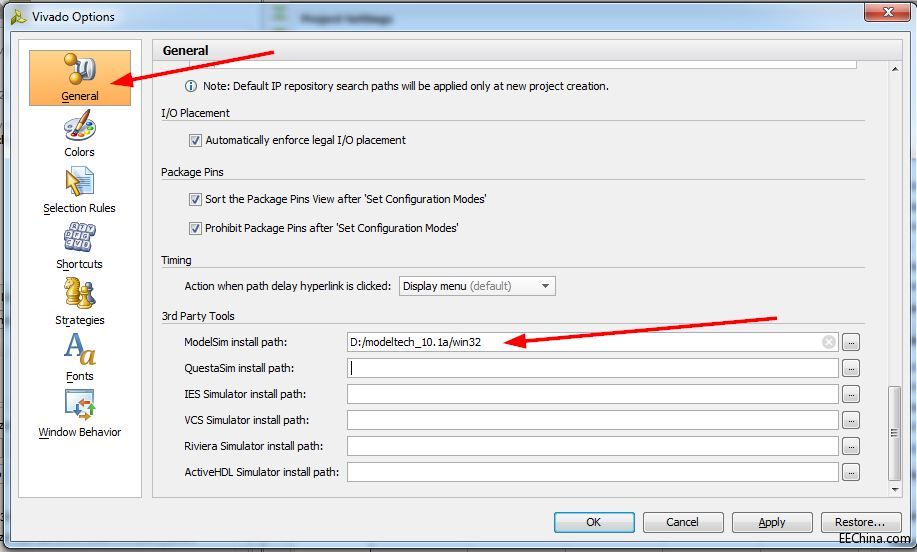

使用Modelsim作为第三方仿真工具,设置也很简单,基本上3步搞定,即设置Modelsim路径、设置Modelsim作为仿真工具、编译器件库。

Modelsim路径设置如图4所示,打开“Tools--> Options...”。

图4 打开Options选项卡

如图5所示,设定已经安装好的Modelsim所在路径。

图5 Modelsim路径设置

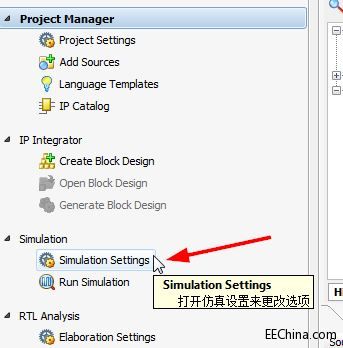

仿真工具的设置,如图6所示,点击"Simulation--> Simulation Settings"。

图6 打开SimulationSettings

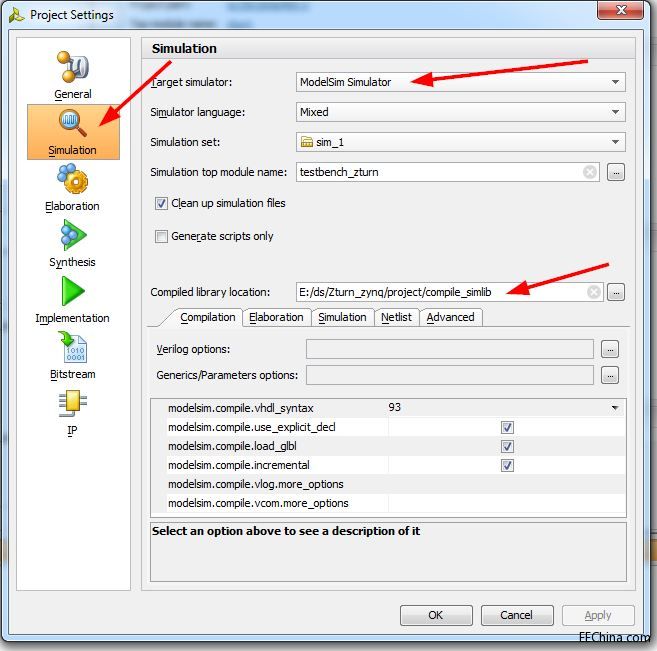

接着如图7所示,设置TargetSimulation为Modelsim Simulator,并且设定第三方工具Modelsim仿真所需Xilinx器件库所存放的路径(Compiled library location)。

图7 SimulationSettings选项卡

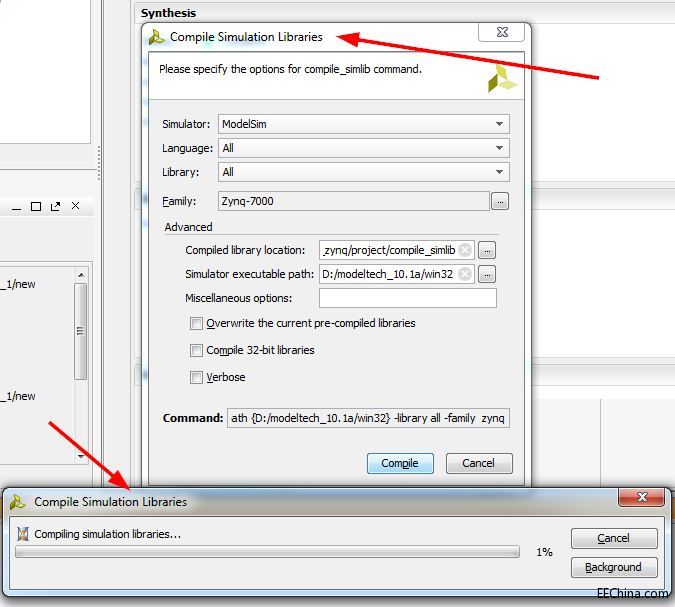

4. 器件库仿真操作

器件库的编译操作也做了一些简化,原先ISE需要多个页面设置,而Vivado浓缩到一个页面,轻轻一点,等着编译完成就可以了。

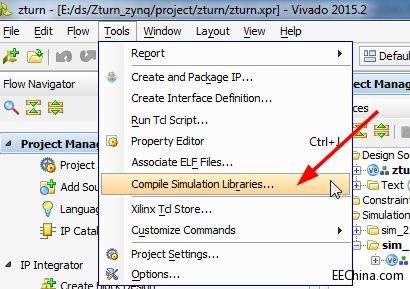

如图8所示,点击打开“CompileSimulation Libraries...”菜单。

图8 打开器件库编译菜单

接着如图9所示设置后,点击“Compile”即可。

图9 器件库编译选项卡

仿真 Altera Xilinx ModelSim 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)