FPGA 101 手把手课堂:让 XDC 时序约束为您效力

时间:01-20

来源:互联网

点击:

物理约束

最常用的物理约束是 I/O 引脚布局和与 I/O 引脚有关的参数定义,例如标准驱动强度。不过,还有其它类型的物理约束,包括布局、布线、I/O 和配置约束等。布局约束能够定义单元的位置,而布线约束可用来定义信号的布线。I/O 约束可用来定义 I/O 位置及其参数。最后,配置约束可用来定义配置方法。

同样,也有一些约束不属于这几组约束。Vivado 设计套件包含三种这样的约束,它们主要用于网表中。

• DONT_TOUCH – 该约束可用来阻止优化,这样当实现安全关键型或高可靠性系统时该约束会非常有用。

• MARK_DEBUG – 该约束可用来保存 RTL信号,以便随后用于调试。

• CLOCK_DEDICATED_ROUTE – 该约束可用来识别时钟布线。

最常用的约束与 I/O 布局和 I/O 的配置有关。将 I/O 放在 FPGA 上,需要使用布局约束找到物理引脚,使用 I/O 约束配置 I/O 标准和斜率等 I/O 属性。

现代化的 FPGA 支持多种单端和差分 I/O 标准。这些均可通过 I/O 约束来进行定义。不过,您必须确保遵守 I/O Banking 规则,这取决于最后的引脚布局。

但什么是 I/O Banking 规则?将 FPGA 中的用户 I/O 分组为若干个 Bank,每个 Bank 包含多组 I/O。这些 Bank 具有独立的电压源,能支持多种 I/O 标准。在 Zynq®-7000 All Programmable SoC(以及其它 7 系列器件)中,I/O Bank 被进一步分为高性能和大范围这两个大的组别。这种类别划分能进一步约束性能,并要求工程师针对接口使用正确的类别。

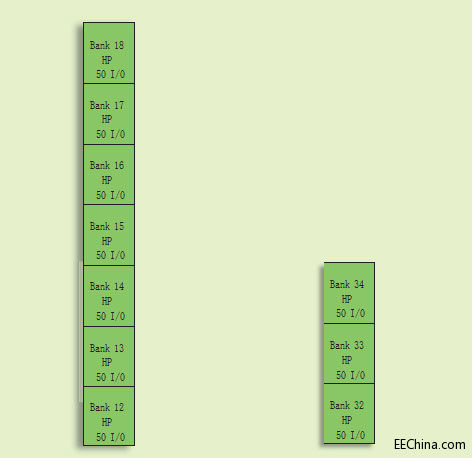

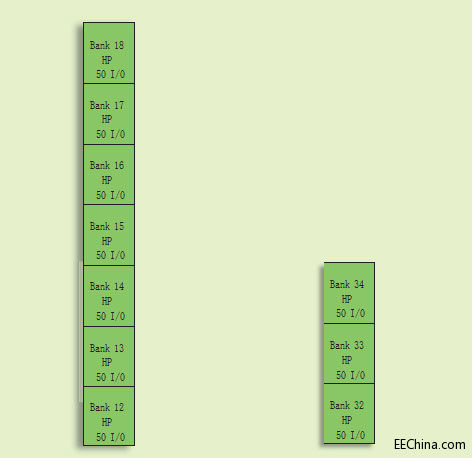

高性能 (HP) 类别针对更高的数据速率进行了精心优化。它使用更低的工作电压,而且不支持 LVCMOS 3v3 和 2v5。另一个是大范围 (HR) 类别,其可处理 HP 不支持的更多 I/O 标准。因此,HR 支持传统的 3v3 和 2v5 接口。图 3 给出了这些 Bank。

当您决定为信号使用哪种 Bank 后,仍然可以更改信号驱动强度和斜率。这些都是硬件设计团队很感兴趣的指标,因为他们要努力确保单板的信号完整性达到最优。选择结果还会影响单板设计的时序。为此,您可以使用信号完整性工具。

SI 工具需要 IBIS 模型。当您打开了Impelmented Design时,您可使用 File->Export->Export IBIS 模型选项从 Vivado 工具中提取设计的 IBIS 模型。然后,使用该文件关闭解决系统级 SI 问题和最终 PCB 布局的时序分析。

如果设计团队整体上对 SI 性能以及系统的时序感到满意,您就会得到针对设计中 I/O 的多个约束,如下所示。

set_property PACKAGE_PIN G17 [get_ports {dout}] set_property IOSTAN- DARD LVCMOS33 [get_ports

{dout}]

set_property SLEW SLOW [get_ports {dout}]

set_property DRIVE 4 [get_ ports {dout}]

对于 HP I/O Bank,您还可使用数控阻抗正确做IO端接并增加系统的 SI,无需使用外部端接方案。如果没有信号驱动 I/O,例如将 I/O 连接到外部连接器,这时您还必须考虑 I/O 的影响。这种情况下,您可使用 I/O 约束实现上拉或下拉电阻,以防止由于 FPGA 输入信号悬置而导致系统问题。

当然,您也可以使用物理约束在 I/O block 内放置最终的输出触发器,以改善设计的时序。这样做能缩短clock to out的时间。您也可以对输入信号做相同的处理,以使设计满足引脚到引脚的建立和保持时间要求。

物理约束从布局开始

您可能出于多种原因想对布局进行约束,例如帮助达到时序要求,或者在设计的不同区域间实现隔离。就此而言,有三种类型的约束很重要:

• BEL –将网表单元放在 slice 中的基本的逻辑元素。

• LOC –将网表的单元放在器件内的一个位置。

• PBlock – 可使用物理(或“P”)block 将逻辑 block 约束到 FPGA 的一个区域。

因此,LOC 允许在器件内定义一个 slice 或其它位置;BEL 约束可用来定义触发器在 slice 中使用的更精细粒度。当对设计的大面积区域进行分段时,PBlock 可用来将逻辑集合在一起。PBlock 的另一个用途是在执行部分重配置时定义逻辑区域。

有些情况下,您需要将较小的逻辑功能放在一组,以确保时序达到最佳。尽管可以用 PBlock 来实现,但更常见的方法是使用相对放置的宏命令。

相对放置的宏命令(RPM)允许将 DSP、触发器、LUT 和 RAM 等设计元素在布局中放在一起。

图 3 – 赛灵思 7 系列器件上的高性能(左)和大范围 I/O Bank

SIGNAL ip_sync :STD_LOGIC_VECTOR(1 DOWNTO 0) :=(OTHERS =>’0’); SIGNEL shr_reg :STD_LOGIC_VECTOR(31 DOWNTO 0) :=(OTHERS =>’0’);

ATTRIBUTE RLOC :STRING; ATTRIBUTE HU_SET :STRING;

ATTRIBUTE HU_SET OF ip_sync :SIGNAL IS “ip_sync”; ATTRIBUTE HU_SET of shr_reg :SIGNAL IS “shr_reg”;

图 4 – 源代码中的约束

• RLOC给定义好的SET分配相对位置。

RLOC 约束被定义为 RLOC = XmYm,其中 X 和 Y 与 FPGA 阵列的坐标有关。当定义 RLOC 时,既可以用相对坐标也可以用绝对坐标,取决于您是否添加了 RPM_GRID 属性。添加这个属性后,该定义将成为绝对坐标而非相对的。由于这些约束在 HDL 中定义,如图 4 所示,因此在将约束添加到 HDL 文件之前,与 PBlock 不同,RPM 不会将这些元素的位置约束在器件的特定区域(除非您想这样做),而是在布局时将这些元素放在一起。

将设计元素放在一起能实现两个目标。这样能改善资源效率,让您能够精细调节互联长度,以实现更好的时序性能。

要将设计元素放在一起,可使用三种类型的约束,这些约束用 HDL 源文件进行定义。

• U_SET 可定义一个与层级无关的单元 RPM 集。

• HU_SET 可定义有层级的单元 RPM 集。

通常需要首先运行布局布线设计反复,以便正确定义布局。

总之,理解时序和布局约束并学习如何正确使用它们,对于在赛灵思可编程逻辑设计中获得最佳结果质量至关重要。

最常用的物理约束是 I/O 引脚布局和与 I/O 引脚有关的参数定义,例如标准驱动强度。不过,还有其它类型的物理约束,包括布局、布线、I/O 和配置约束等。布局约束能够定义单元的位置,而布线约束可用来定义信号的布线。I/O 约束可用来定义 I/O 位置及其参数。最后,配置约束可用来定义配置方法。

同样,也有一些约束不属于这几组约束。Vivado 设计套件包含三种这样的约束,它们主要用于网表中。

• DONT_TOUCH – 该约束可用来阻止优化,这样当实现安全关键型或高可靠性系统时该约束会非常有用。

• MARK_DEBUG – 该约束可用来保存 RTL信号,以便随后用于调试。

• CLOCK_DEDICATED_ROUTE – 该约束可用来识别时钟布线。

最常用的约束与 I/O 布局和 I/O 的配置有关。将 I/O 放在 FPGA 上,需要使用布局约束找到物理引脚,使用 I/O 约束配置 I/O 标准和斜率等 I/O 属性。

现代化的 FPGA 支持多种单端和差分 I/O 标准。这些均可通过 I/O 约束来进行定义。不过,您必须确保遵守 I/O Banking 规则,这取决于最后的引脚布局。

但什么是 I/O Banking 规则?将 FPGA 中的用户 I/O 分组为若干个 Bank,每个 Bank 包含多组 I/O。这些 Bank 具有独立的电压源,能支持多种 I/O 标准。在 Zynq®-7000 All Programmable SoC(以及其它 7 系列器件)中,I/O Bank 被进一步分为高性能和大范围这两个大的组别。这种类别划分能进一步约束性能,并要求工程师针对接口使用正确的类别。

高性能 (HP) 类别针对更高的数据速率进行了精心优化。它使用更低的工作电压,而且不支持 LVCMOS 3v3 和 2v5。另一个是大范围 (HR) 类别,其可处理 HP 不支持的更多 I/O 标准。因此,HR 支持传统的 3v3 和 2v5 接口。图 3 给出了这些 Bank。

当您决定为信号使用哪种 Bank 后,仍然可以更改信号驱动强度和斜率。这些都是硬件设计团队很感兴趣的指标,因为他们要努力确保单板的信号完整性达到最优。选择结果还会影响单板设计的时序。为此,您可以使用信号完整性工具。

SI 工具需要 IBIS 模型。当您打开了Impelmented Design时,您可使用 File->Export->Export IBIS 模型选项从 Vivado 工具中提取设计的 IBIS 模型。然后,使用该文件关闭解决系统级 SI 问题和最终 PCB 布局的时序分析。

如果设计团队整体上对 SI 性能以及系统的时序感到满意,您就会得到针对设计中 I/O 的多个约束,如下所示。

set_property PACKAGE_PIN G17 [get_ports {dout}] set_property IOSTAN- DARD LVCMOS33 [get_ports

{dout}]

set_property SLEW SLOW [get_ports {dout}]

set_property DRIVE 4 [get_ ports {dout}]

对于 HP I/O Bank,您还可使用数控阻抗正确做IO端接并增加系统的 SI,无需使用外部端接方案。如果没有信号驱动 I/O,例如将 I/O 连接到外部连接器,这时您还必须考虑 I/O 的影响。这种情况下,您可使用 I/O 约束实现上拉或下拉电阻,以防止由于 FPGA 输入信号悬置而导致系统问题。

当然,您也可以使用物理约束在 I/O block 内放置最终的输出触发器,以改善设计的时序。这样做能缩短clock to out的时间。您也可以对输入信号做相同的处理,以使设计满足引脚到引脚的建立和保持时间要求。

物理约束从布局开始

您可能出于多种原因想对布局进行约束,例如帮助达到时序要求,或者在设计的不同区域间实现隔离。就此而言,有三种类型的约束很重要:

• BEL –将网表单元放在 slice 中的基本的逻辑元素。

• LOC –将网表的单元放在器件内的一个位置。

• PBlock – 可使用物理(或“P”)block 将逻辑 block 约束到 FPGA 的一个区域。

因此,LOC 允许在器件内定义一个 slice 或其它位置;BEL 约束可用来定义触发器在 slice 中使用的更精细粒度。当对设计的大面积区域进行分段时,PBlock 可用来将逻辑集合在一起。PBlock 的另一个用途是在执行部分重配置时定义逻辑区域。

有些情况下,您需要将较小的逻辑功能放在一组,以确保时序达到最佳。尽管可以用 PBlock 来实现,但更常见的方法是使用相对放置的宏命令。

相对放置的宏命令(RPM)允许将 DSP、触发器、LUT 和 RAM 等设计元素在布局中放在一起。

图 3 – 赛灵思 7 系列器件上的高性能(左)和大范围 I/O Bank

SIGNAL ip_sync :STD_LOGIC_VECTOR(1 DOWNTO 0) :=(OTHERS =>’0’); SIGNEL shr_reg :STD_LOGIC_VECTOR(31 DOWNTO 0) :=(OTHERS =>’0’);

ATTRIBUTE RLOC :STRING; ATTRIBUTE HU_SET :STRING;

ATTRIBUTE HU_SET OF ip_sync :SIGNAL IS “ip_sync”; ATTRIBUTE HU_SET of shr_reg :SIGNAL IS “shr_reg”;

图 4 – 源代码中的约束

• RLOC给定义好的SET分配相对位置。

RLOC 约束被定义为 RLOC = XmYm,其中 X 和 Y 与 FPGA 阵列的坐标有关。当定义 RLOC 时,既可以用相对坐标也可以用绝对坐标,取决于您是否添加了 RPM_GRID 属性。添加这个属性后,该定义将成为绝对坐标而非相对的。由于这些约束在 HDL 中定义,如图 4 所示,因此在将约束添加到 HDL 文件之前,与 PBlock 不同,RPM 不会将这些元素的位置约束在器件的特定区域(除非您想这样做),而是在布局时将这些元素放在一起。

将设计元素放在一起能实现两个目标。这样能改善资源效率,让您能够精细调节互联长度,以实现更好的时序性能。

要将设计元素放在一起,可使用三种类型的约束,这些约束用 HDL 源文件进行定义。

• U_SET 可定义一个与层级无关的单元 RPM 集。

• HU_SET 可定义有层级的单元 RPM 集。

通常需要首先运行布局布线设计反复,以便正确定义布局。

总之,理解时序和布局约束并学习如何正确使用它们,对于在赛灵思可编程逻辑设计中获得最佳结果质量至关重要。

FPGA 赛灵思 SoC 电压 CMOS PCB 连接器 电阻 DSP 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)