基于FPGA的结构光图像中心线提取

时间:12-03

来源:互联网

点击:

摘要:在线结构光视觉三维测量系统中,为了实现对结构光图像线条纹中心的实时高精度提取,本文采用了极值法、阈值法和灰度重心法相结合的中心线提取方法。利用现场可编程门阵列器件(FPGA)的流水线技术以及并行技术的硬件设计来完成运算,保证了光条纹中心点的实时准确提取。实验表明采用FPGA 实现图像处理的专用算法能满足图像数据进行实时准确提取的要求。

引言

随着测控技术及数字图像处理技术的高速发展,基于三角法线结构光的三维测量具有高精度、非接触、实时性和强主动受控性的特性,因此在现实中有广泛的应用,尤其是在计算机视觉、医疗诊断和工业检测等领域应用价值日渐增强。在结构光检测系统中,利用CCD相机以及工业相机摄取用线结构平面激光照射照在物体表面形成的光条纹中心信息,然后根据光条纹中心偏移量进行三维定标,这样可以得到物体表面的各类信息,比如表面的缺陷以及形变等。有鉴于此,线结构光条中心信息的图像处理在测量过程中就显得十分关键[1-3]。虽然目前结构光中心线的提取方法有许多种,比如:阈值法、极值法、灰度重心法、方向模板法、Hessian矩阵法等[4-6],这些方法都有各自的优缺点以及一定的应用范围。基于数字图像处理的特点是处理的数据量非常大,处理非常耗时。所以本文研究了在FPGA上用硬件描述语言实现图像的中心线提取算法,采用了极值法、阈值法和重心法相结合的中心线提取方法。通过功能模块的硬件化,以便高速提取结构光中心线。结果表明,实验系统达到了基于视频速度的应用要求。

1 系统硬件设计

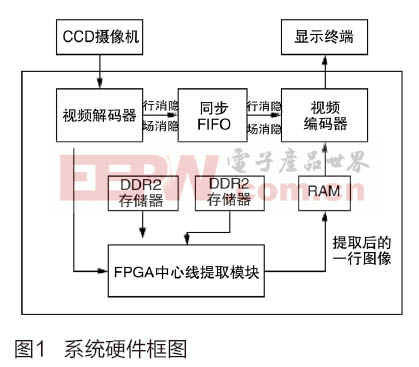

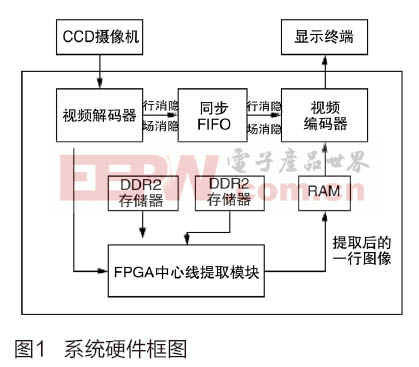

图1为光条中心线提取系统的硬件设计框图。整个中心线提取系统主要有四个组成部分:

(1)视频数据编码模块:编码器采用ANALOG DEVICES公司的ADV7179芯片,该编码器能实现ITU—R BT601/BT656 YCrCb(其比例为4:2:2)格式的数字信号转为NTSC/PAL摸拟视频输出信号;

(2)DDR2 SDRAM存储器控制模块:选用两片MICRON公司的MT47H64M16 DDR2存储器来实现图像帧数的交叉缓存,为后面的中心线提取提供像素值以及坐标值;

(3)中心线提取模块:FPGA采用的是Altera公司Cyclone III系列的EP3C40F484C6芯片,该芯片价格低廉、实用性强,能充分发挥芯片的并行计算能力,实现中心线的快速提取;

(4)视频数据编解码模块:解码器采用TEXAS INSTRUMENT 公司的TVP5150芯片,该芯片低功耗,能解决视频输入输出同步问题,而且输出型号的特性可以通过I2C串行接口进行编程配置。

整个系统从CCD摄像机接收的模拟视频信号通过视频解码芯片解码后,转换成BT656(4:2:2)YCbCr SDTV(标清)格式的数字视频信号,通过一个FIFO来进行行/场消隐、解出同步信息等操作,之后提取图像信息的Y(亮度值)分量,然后在数据上传输。对于图像的传送采用两片DDR2来进行奇偶两场传送;同时对视频解码器输出的同步信号进行检测。当有效数据到来时,FPGA选择一片DDR2,使用隔行存储方式,完成一帧图像的存储,当第二帧图像有效数据到来时,FPGA选择另一片DDR2,以相同的方式完成第二帧图像的存储,依次交叉存储,然后经内部的处理模块处理后得到图像光带中心线坐标[8]。将提取的一行中心线坐标存储在RAM里面,再经过视频编码器将数字视频信号转换成模拟视频信号输出到显示终端显示。

2 算法的FPGA实现

2.1 算法流程

我们首先以列扫描的方式读出一帧数据,并将读出的亮度值与所设定的阈值进行比较。滤除不需要的点,然后通过像素值比较得到像素值最大点,之后用最大点周边的3*3邻接点来进行灰度重心法计算出光条中心点。具体做法如下:

(1)由于光带图像中的亮点太多,所以对读出的像素值与设定的阈值进行比较,滤除杂点;

(2)对大于阈值的点进行比较,找到亮度值最大的点

及其周边3*3邻域点;

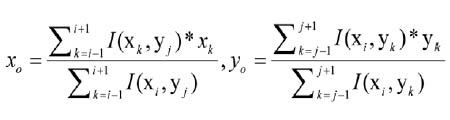

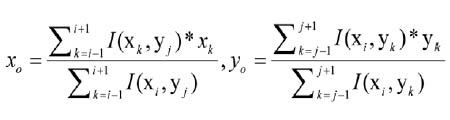

(3)然后,对 分别运用(1)式求得其亚像素坐标:

(1)2.2 存储单元

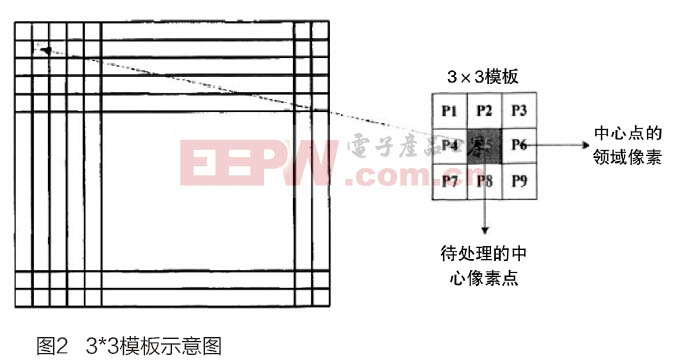

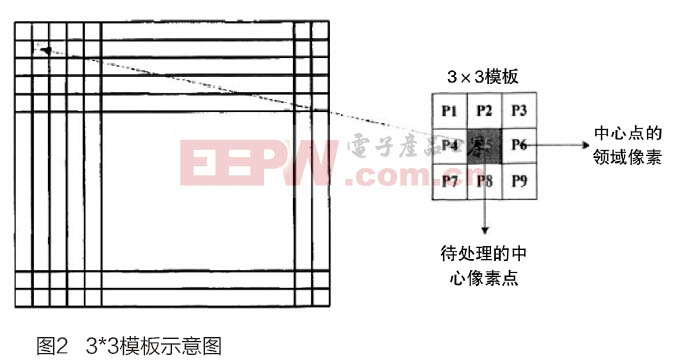

对于算法的实现,还要考虑图像数据的存储结构。这其中包括:点存储器,用来存储需要运算的单个像素点;行存储器,用来缓存需要运算的图像的一行像素点;帧存储器,用来存储整帧图像。一般帧存储器都需要很大的容量,而FPGA内部实现起来比较困难,所以FPGA板都会增加外部存储器,由外部的DDR2 SDRAM 芯片实现[9];为了使进行运算的领域9个3*3的像素点能在同一时钟输出,便于进行之后的流水线算法模块,因此在3*3的滑动窗的硬件设计中,本文采用了2个RAM存储器来进行行存储。具体操作是:先用两个RAM存储器存储两行数据,等到第三行到来时,再将前两行的数据读出来,之后用9个寄存器存储这9个数据,以保证数据的同时获取[10]。存储结构见图2所示。

这样,当图像像素点串行输入时,经过这种结构的存储器系统,即可得到相应点进行灰度重心法计算所需的所有邻域点的并行输出。

2.3 运算单元

运算单元由乘法器和流水线加法树两部分构成,乘法器的作用是执行运算中的坐标值与像素相乘,流水线加法树的作用是提高运算速度以及减少运算单元占用的硬件资源,该加法数设计为4段流水线结构,第一段为6个2输入的8位乘法器和2个2输入的8位加法器以及2个延迟单元;第二段为2个2输入的15位加法器和2个2输入的9位加法器以及2个延迟单元;第三段为2个2输入的16位加法器和2个延迟单元;第四段为2个除法器,作用是将运算的像素与像素坐标值的乘积累加后除以运算的像素的累加值,输出的结果即为中心点 的坐标值。运算如图3和图4所示。

引言

随着测控技术及数字图像处理技术的高速发展,基于三角法线结构光的三维测量具有高精度、非接触、实时性和强主动受控性的特性,因此在现实中有广泛的应用,尤其是在计算机视觉、医疗诊断和工业检测等领域应用价值日渐增强。在结构光检测系统中,利用CCD相机以及工业相机摄取用线结构平面激光照射照在物体表面形成的光条纹中心信息,然后根据光条纹中心偏移量进行三维定标,这样可以得到物体表面的各类信息,比如表面的缺陷以及形变等。有鉴于此,线结构光条中心信息的图像处理在测量过程中就显得十分关键[1-3]。虽然目前结构光中心线的提取方法有许多种,比如:阈值法、极值法、灰度重心法、方向模板法、Hessian矩阵法等[4-6],这些方法都有各自的优缺点以及一定的应用范围。基于数字图像处理的特点是处理的数据量非常大,处理非常耗时。所以本文研究了在FPGA上用硬件描述语言实现图像的中心线提取算法,采用了极值法、阈值法和重心法相结合的中心线提取方法。通过功能模块的硬件化,以便高速提取结构光中心线。结果表明,实验系统达到了基于视频速度的应用要求。

1 系统硬件设计

图1为光条中心线提取系统的硬件设计框图。整个中心线提取系统主要有四个组成部分:

(1)视频数据编码模块:编码器采用ANALOG DEVICES公司的ADV7179芯片,该编码器能实现ITU—R BT601/BT656 YCrCb(其比例为4:2:2)格式的数字信号转为NTSC/PAL摸拟视频输出信号;

(2)DDR2 SDRAM存储器控制模块:选用两片MICRON公司的MT47H64M16 DDR2存储器来实现图像帧数的交叉缓存,为后面的中心线提取提供像素值以及坐标值;

(3)中心线提取模块:FPGA采用的是Altera公司Cyclone III系列的EP3C40F484C6芯片,该芯片价格低廉、实用性强,能充分发挥芯片的并行计算能力,实现中心线的快速提取;

(4)视频数据编解码模块:解码器采用TEXAS INSTRUMENT 公司的TVP5150芯片,该芯片低功耗,能解决视频输入输出同步问题,而且输出型号的特性可以通过I2C串行接口进行编程配置。

整个系统从CCD摄像机接收的模拟视频信号通过视频解码芯片解码后,转换成BT656(4:2:2)YCbCr SDTV(标清)格式的数字视频信号,通过一个FIFO来进行行/场消隐、解出同步信息等操作,之后提取图像信息的Y(亮度值)分量,然后在数据上传输。对于图像的传送采用两片DDR2来进行奇偶两场传送;同时对视频解码器输出的同步信号进行检测。当有效数据到来时,FPGA选择一片DDR2,使用隔行存储方式,完成一帧图像的存储,当第二帧图像有效数据到来时,FPGA选择另一片DDR2,以相同的方式完成第二帧图像的存储,依次交叉存储,然后经内部的处理模块处理后得到图像光带中心线坐标[8]。将提取的一行中心线坐标存储在RAM里面,再经过视频编码器将数字视频信号转换成模拟视频信号输出到显示终端显示。

2 算法的FPGA实现

2.1 算法流程

我们首先以列扫描的方式读出一帧数据,并将读出的亮度值与所设定的阈值进行比较。滤除不需要的点,然后通过像素值比较得到像素值最大点,之后用最大点周边的3*3邻接点来进行灰度重心法计算出光条中心点。具体做法如下:

(1)由于光带图像中的亮点太多,所以对读出的像素值与设定的阈值进行比较,滤除杂点;

(2)对大于阈值的点进行比较,找到亮度值最大的点

及其周边3*3邻域点;

(3)然后,对 分别运用(1)式求得其亚像素坐标:

(1)2.2 存储单元

对于算法的实现,还要考虑图像数据的存储结构。这其中包括:点存储器,用来存储需要运算的单个像素点;行存储器,用来缓存需要运算的图像的一行像素点;帧存储器,用来存储整帧图像。一般帧存储器都需要很大的容量,而FPGA内部实现起来比较困难,所以FPGA板都会增加外部存储器,由外部的DDR2 SDRAM 芯片实现[9];为了使进行运算的领域9个3*3的像素点能在同一时钟输出,便于进行之后的流水线算法模块,因此在3*3的滑动窗的硬件设计中,本文采用了2个RAM存储器来进行行存储。具体操作是:先用两个RAM存储器存储两行数据,等到第三行到来时,再将前两行的数据读出来,之后用9个寄存器存储这9个数据,以保证数据的同时获取[10]。存储结构见图2所示。

这样,当图像像素点串行输入时,经过这种结构的存储器系统,即可得到相应点进行灰度重心法计算所需的所有邻域点的并行输出。

2.3 运算单元

运算单元由乘法器和流水线加法树两部分构成,乘法器的作用是执行运算中的坐标值与像素相乘,流水线加法树的作用是提高运算速度以及减少运算单元占用的硬件资源,该加法数设计为4段流水线结构,第一段为6个2输入的8位乘法器和2个2输入的8位加法器以及2个延迟单元;第二段为2个2输入的15位加法器和2个2输入的9位加法器以及2个延迟单元;第三段为2个2输入的16位加法器和2个延迟单元;第四段为2个除法器,作用是将运算的像素与像素坐标值的乘积累加后除以运算的像素的累加值,输出的结果即为中心点 的坐标值。运算如图3和图4所示。

FPGA 编码器 Altera 解码器 Verilog 仿真 电路 机器视觉 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)